#### Workshop on Essential Abstractions in GCC

## Advanced Issues in Machine Descriptions

GCC Resource Center (www.cse.iitb.ac.in/grc)

Department of Computer Science and Engineering, Indian Institute of Technology, Bombay

July 2010

#### Outline

- Some details of MD constructs

- ▶ On names of patterns in .md files

- ▶ On the role of define\_expand

- On the role of constraints

- Mode and code iterators

- Defining attributes

- Other constructs

- Improving machine descriptions and instruction selection

- ▶ New constructs to factor out redundancy

- ▶ Tree tiling based instruction selection

#### Part 1

## Some Details of MD Constructs

2/27

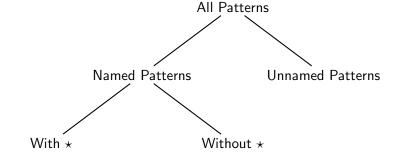

# All Patterns

Named Patterns Unnamed Patterns

Advanced MD Issues: Some Details of MD Constructs

Advanced MD Issues: Some Details of MD Constructs

#### rattern rames in that the

#### rattern rames in .ma rine

Advanced MD Issues: Some Details of MD Constructs

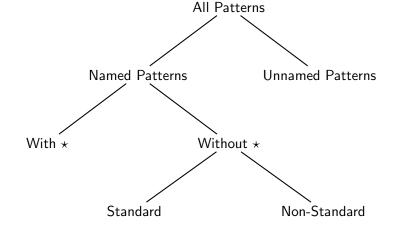

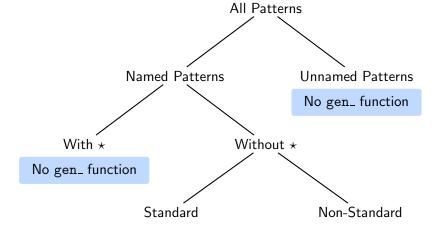

All Patterns

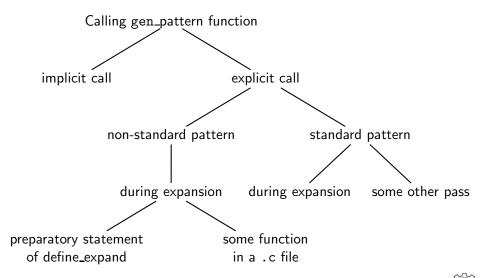

Named Patterns Unnamed Patterns No gen\_ function With \* Without \* No gen\_ function Non-Standard Standard gen\_name function gen\_name function Called implicitly Not called implicitly Can be called explicitly Can be called explicitly

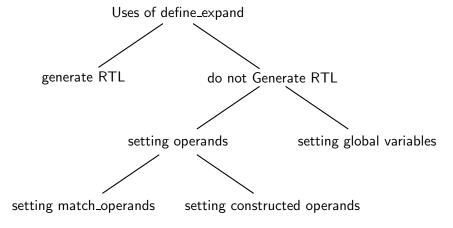

## Role of define\_expand

### Using define\_expand for Generating RTL statements

Advanced MD Issues: Some Details of MD Constructs

July 2010

5/27

# Understanding Constraints

# **Understanding Constraints**

5/27

# Understanding Constraints

Reloading operands in the most suitable register class

- Reloading operands in the most suitable register class

- Fine tuning within the set of operands allowed by the predicate

5/27

# Understanding Constraints

- Reloading operands in the most suitable register class

- Fine tuning within the set of operands allowed by the predicate

- If omitted, operands will depend only on the predicates

### Observations - Role of Constraints

Consider the following two instruction patterns:

The destination and left operands must be identical

## Role of Constraints

Consider an insp of the form

```

(insn n prev next

(set (reg:SI 3)

(plus:SI (reg:SI 6) (reg:SI 109)))

...)}

```

- Predicates of the first pattern does not match

- Constraints do not match for first operand of the second pattern

## Role of Constraints

Consider an insn of the form

```

(insn n prev next

(set (reg:SI 3)

(plus:SI (reg:SI 6) (reg:SI 109)))

...)}

```

- Predicates of the first pattern does not match

- Constraints do not match for first operand of the second pattern

- Reload pass generates additional insn to that the first pattern can be used

#### Observations: Constraints

Advanced MD Issues: Some Details of MD Constructs

• define\_insns patterns have operand predicates and constraints

8/27

July 2010

## **Observations: Constraints**

- define\_insns patterns have operand predicates and constraints

- While generating the RTL from GIMPLE only the operand predicates are checked and the constraints are completely ignored

## Observations: Constraints

- define\_insns patterns have operand predicates and constraints

- While generating the RTL from GIMPLE only the operand predicates are checked and the constraints are completely ignored

- The RTL which is generated in the expander is modified in the reload pass to fulfil the constraint

- define\_insns patterns have operand predicates and constraints

- While generating the RTL from GIMPLE only the operand predicates are checked and the constraints are completely ignored

- The RTL which is generated in the expander is modified in the reload pass to fulfil the constraint

- This final form of RTL can be generated in expander by using constraints early

9/27

Advanced MD Issues: Some Details of MD Constructs

```

(define_insn "subsi3"

```

July 2010

```

"subu\t %0,%1,%2"

[(set_attr "type" "arith")

(set_attr "mode" "SI")])

```

```

(match_operand:DI 2 "register_operand" "d")))]

""

"dsubu\t %0,%1,%2"

[(set_attr "type" "arith")

```

(minus:SI (match\_operand:SI 1 "register\_operand" "d")

9/27

Advanced MD Issues: Some Details of MD Constructs

```

[(set (match_operand:DI 0 "register_operand" "=d")

(minus:DI (match_operand:DI 1 "register_operand" "d")

```

44 77

44 77

(define insn "subsi3"

July 2010

```

(match_operand:SI 2 "register_operand" "d")))]

"subu\t %0,%1,%2"

[(set_attr "type" "arith")

(set_attr "mode" "SI")])

(define_insn "subdi3"

```

[(set (match\_operand:SI 0 "register\_operand" "=d")

GCC Resource Center, IIT Bomba

# Mode Iterators: Abstracting Out Mode Differences

```

(define_mode_iterator GPR [SI (DI "TARGET_64BIT")])

(define_mode_attr d [(SI "")(DI "d")])

(define_insn "sub<mode>3"

[(set (match_operand:GPR 0 "register_operand" "=d")

(minus:GPR (match_operand:GPR 1 "register_operand" "d")

(match_operand:GPR 2 "register_operand" "d")))]

44 77

"<d>subu\t %0,%1,%2"

[(set_attr "type" "arith")

(set_attr "mode" "<MODE>")])

```

Advanced MD Issues: Some Details of MD Constructs

11/27

44 77

})

DONE:

July 2010

```

(define_expand "bunordered"

[(set (pc) (if_then_else (unordered:CC (cc0) (const_int 0))

(label_ref (match_operand 0 ""))

(pc)))]

{ mips_expand_conditional_branch (operands, UNORDERED);

(define_expand "bordered"

[(set (pc) (if_then_else (ordered:CC (cc0) (const_int 0))

(label_ref (match_operand 0 ""))

(pc)))]

mips_expand_conditional_branch (operands, ORDERED);

```

11/27

Advanced MD Issues: Some Details of MD Constructs

[(set (pc) (if\_then\_else (unordered:CC (cc0) (const\_int 0))

```

(label_ref (match_operand 0 ""))

(pc)))]

44 77

{ mips_expand_conditional_branch (operands, UNORDERED);

DONE:

})

(define_expand "bordered"

[(set (pc) (if_then_else (ordered:CC (cc0) (const_int 0))

(label_ref (match_operand 0 ""))

(pc)))]

44 11

mips_expand_conditional_branch (operands, ORDERED);

DONE;

```

July 2010

12/27

Advanced MD Issues: Some Details of MD Constructs

```

(define_code_iterator any_cond [unordered ordered])

(define_expand "b<code>"

[(set (pc)

(if_then_else (any_cond:CC (cc0)

(const_int 0))

(label_ref (match_operand 0

(pc)))]

44 11

mips_expand_conditional_branch (operands, <CODE>);

DONE;

```

13/27

## Defining Attributes

- Classifications are need based

- Useful to GCC phases e.g. pipelining

Property: Pipelining

Need: To classify target instructions

Construct: define\_attr

- Classifications are need based

- Useful to GCC phases e.g. pipelining

Property: Pipelining Need: To classify target instructions

Construct: define attr

```

Instruction type.

```

(define\_attr "type"

"other, multi, alu, alu1, negnot,

(const\_string "other") )

str ,cld, ..."

13/27

# **Defining Attributes**

- Classifications are need based

- Useful to GCC phases e.g. pipelining

Property: Pipelining

Need: To classify target instructions

Construct: define attr

Instruction type.

(define\_attr "type"

"other, multi, alu, alu1, negnot,

(const\_string "other") )

str ,cld, ..."

Attribute name,

Fields:

13/27

### **Defining Attributes**

Useful to GCC phases – e.g. pipelining

Classifications are need based

Property: Pipelining

"other, multi, alu, alu1, negnot,

Need: To classify target instructions

Construct: define attr

Instruction type.

(define\_attr "type"

Fields:

(const\_string "other")

Attribute name, all possible values,

str ,cld, ..."

13/27

## Defining Attributes

- Classifications are need based

- Useful to GCC phases e.g. pipelining

Property: Pipelining

Need: To classify target instructions

(const\_string "other") )

Construct: define\_attr

;; Instruction type.

(define\_attr "type"

"other, multi, alu, alu1, negnot,

Fields:

Attribute name, all possible values, one of the possible values,

ay (i)

str ,cld, ..."

str ,cld, ..."

13/27

- Classifications are need based

- Useful to GCC phases e.g. pipelining

Property: Pipelining

Need: To classify target instructions

Construct: define\_attr

;; Instruction type.

(define\_attr "type"

(derine\_acti type

"other, multi, alu, alu1, negnot, ...

(const\_string "other") )

ماطم

Fields:

Attribute name, all possible values, one of the possible values, default.

Essential Abstractions in GCC GCC Resource Center, IIT Bomba

- Optional field of a define\_insn

- For an i386, we choose to mark string instructions with the attribute value str

Advanced MD Issues: Some Details of MD Constructs

```

(define_insn "*strmovdi_rex_1"

[(set (mem:DI (match_operand:DI 2 ...)]

"TARGET_64BIT && (TARGET_SINGLE_ ...)"

"movsq"

[ (set_attr "type" "str")

(set_attr "memory" "both")])

```

#### NOTE

An instruction may have more than one attribute!

15/27

(define\_insn\_reservation "pent\_str" 12

Pipeline specification requires the CPU type to be "pentium" and the instruction type to be "str"

# Some Other RTL Constructs

- define\_split: Split complex insn into simpler ones e.g. for better use of delay slots

- define\_insn\_and\_split: A combination of define\_insn and define\_split Used when the split pattern matches and insn exactly.

- define\_peephole2: Peephole optimization over insns that substitutes insns. Run after register allocation, and before scheduling.

- define\_constants: Use literal constants in rest of the MD.

#### Part 2

# Improving Instruction Selection and Machine Descriptions

Advanced MD Issues: Improving MD and Instruction Selection

**Improving Machine Descriptions and Instruction Selection**

July 2010

- Instruction selection algorithms are quite adhoc

- The specification mechanism for Machine descriptions is quite adhoc

Adhoc design decisions

Advanced MD Issues: Improving MD and Instruction Selection

**Improving Machine Descriptions and Instruction Selection**

The Problem

July 2010

- Instruction selection algorithms are quite adhoc

- Full tree maching instead of tree tiling

- The specification mechanism for Machine descriptions is quite adhoc

Adhoc design decisions

# **Improving Machine Descriptions and Instruction Selection**

#### The Problems:

- Instruction selection algorithms are quite adhoc

- Full tree maching instead of tree tiling

- The specification mechanism for Machine descriptions is quite adhoc

- Only syntax borrowed from LISP, neither semantics not spirit!

- Non-composable rules

- Mode and code iterator mechanisms are insufficient

- Adhoc design decisions

# The Problems:

- Instruction selection algorithms are quite adhoc

- Full tree maching instead of tree tiling

- The specification mechanism for Machine descriptions is quite adhoc

- Only syntax borrowed from LISP, neither semantics not spirit!

- Non-composable rules

- Mode and code iterator mechanisms are insufficient

- Adhoc design decisions

- ► Honouring operand constraints delayed to global register allocation During GIMPLE to RTL translation, a lot of C code is required

- Choice of insertion of NOPs

# **Design Flaws in Machine Descriptions**

#### Multiple patterns with same structure

- Repetition of almost similar RTL expressions across multiple define\_insn an define\_expand patterns

- Only Modes, Predicates, Constraints, Boolean Condition, or RTL Expression may differ

- One RTL expression may appears as a sub-expression of some other RTL expression

- Repetition of C code along with RTL expressions in these patterns.

# Consequence of Design Flaws in Machine Descriptions

- The machine descriptions are too verbose, detailed, repetitive and require a lot of C code

- A compiler developer needs to visualize and specify meaningful combinations of instructions for generating good quality code

- The machine descriptions are difficult to construct, understand, maintain, and enhance

- GCC has become a hacker's paradise instead of a clean, production quality compiler generation framework

## Insufficient Iterator Mechanism

- Iterators can not be used across define\_insn, define\_expand, define\_peephole2 and other patterns

- Defining iterator attribute for each varying parameter becomes tedious.

- For same set of modes and rtx codes change in other fields of pattern makes use of iterators impossible

- Mode and code attributes can not be defined for operator or operand number, name of the pattern.

- Patterns with different RTL template share attribute value vector for which iterators can not be used.

```

[(set (match_operand:DI 0 "nonimmediate_operand" "")

(ior:DI (match_operand:DI 1 "nonimmediate_operand" "")

(match_operand:DI 2 "x86_64_general_operand" "")))

(clobber (reg:CC FLAGS_REG))]

"TARGET 64BIT"

"ix86_expand_binary_operator (IOR, DImode, operands); DONE;")

```

[(set (match\_operand:DI 0 "nonimmediate\_operand" "=rm,r")

(ior:DI (match\_operand:DI 1 "nonimmediate\_operand" "%0,0")

```

(match_operand:DI 2 "x86_64_general_operand" "re,rme")))

(clobber (reg:CC FLAGS_REG))]

"TARGET 64BIT

&& ix86_binary_operator_ok (IOR, DImode, operands)"

"or{q}\t{%2, %0|%0, %2}"

```

[(set\_attr "type" "alu")

(define\_insn "\*iordi\_1\_rex64"

21/27

July 2010

- New contructs to facilitate more concise machine descriptions

- define\_rtltemplate Introduces non-terminals for common RTL expressions instead of rewriting them in each define\_insn or define\_expand pattern

- define\_code Introduces non-terminals for C/Assembly code instead of rewriting them in each define\_insn or define\_expand pattern

- define\_pattern

Allows specification of multiple define\_insn and define\_expand sharing RTL template, assembly template, or C code

## Step 1: Avoiding Verbosity in Machine Description

- New contructs to facilitate more concise machine descriptions

- define\_rtltemplate defining Introduces non-terminals for common RTL expressions instead of rewriting them in each define\_insn or define\_expand pattern

- ► define\_code defining

Introduces non-terminals for C/Assembly code instead of rewriting

them in each define\_insn or define\_expand pattern

- define\_pattern instantiating Allows specification of multiple define\_insn and define\_expand sharing RTL template, assembly template, or C code

- Generate exisiting machine descriptions from new descriptions

- $\Rightarrow$  No change in GCC source

- ⇒ Incremental changes with gradual transition to new descriptions

- ⇒ Non-disruptive transition

## Improvement Statistics for 'i386.md'

Machine description file i386.md is rewritten. **5720** lines are reduced from current MD specification for 'i386.md(21474 lines). Ignoring the comments this reduction is 28% of the complete MD file.

| Instruction Group             | Instruction   | define_rtItemplate |

|-------------------------------|---------------|--------------------|

| instruction Group             | Pattern count | count              |

| Arithmetic instructions       | 154           | 50                 |

| Control flow and data move    | 626           | 169                |

| instructions                  |               |                    |

| Logical and relational in-    | 212           | 56                 |

| structions                    |               |                    |

| Shift and rotate instructions | 311           | 67                 |

| Total                         | 1303          | 342                |

Improvement statistics in terms of reduction in RTL templates

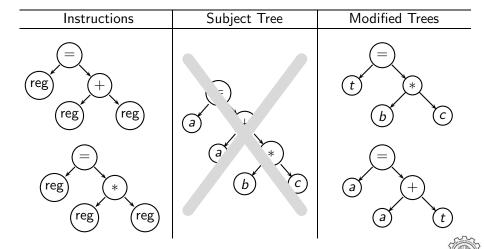

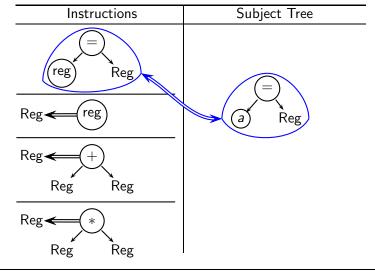

# Step 2: Improving instruction Selection

Advanced MD Issues: Improving MD and Instruction Selection

Since rules become composable, tree tiling based instruction selection algorithms can be used

Currently rules are non-composable and GCC uses full tree maching algorithm

24/27

July 2010

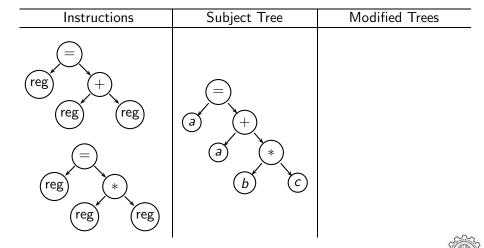

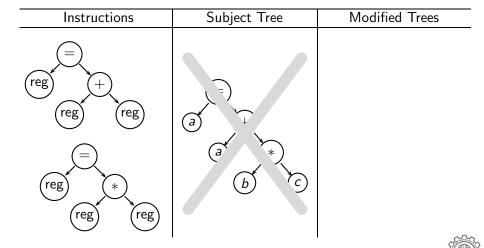

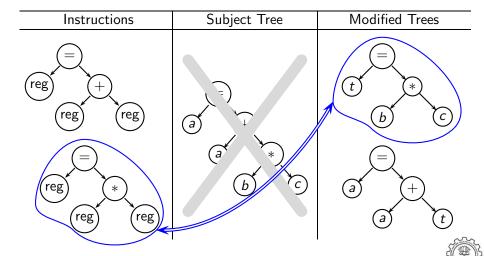

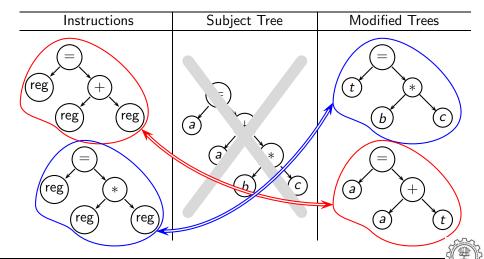

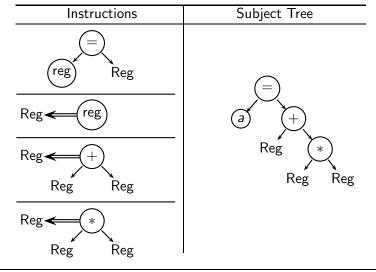

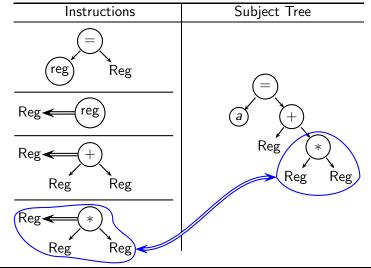

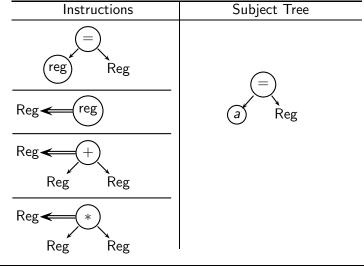

# **Full Tree Matching**

| Instructions | Subject Tree | Modified Trees |

|--------------|--------------|----------------|

| reg + reg    |              |                |

| reg * reg    |              | 200            |

# **Full Tree Matching**

# **Full Tree Matching**

# **Full Tree Matching**

#### **Full Tree Matching**

### Full Tree Matching

Instructions are viewed as composable rules

| Instructions | Subject Tree |

|--------------|--------------|

| reg          |              |

| reg          |              |

| Reg Reg      |              |

| * Reg Reg    |              |

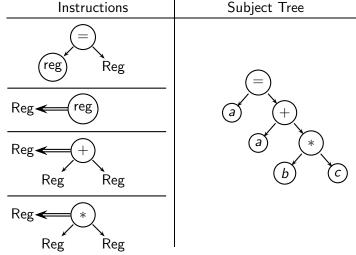

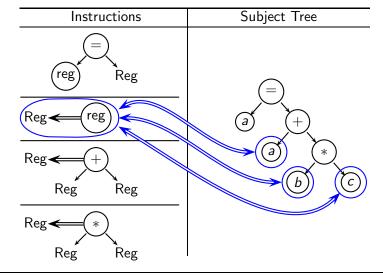

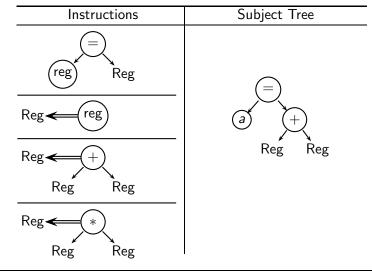

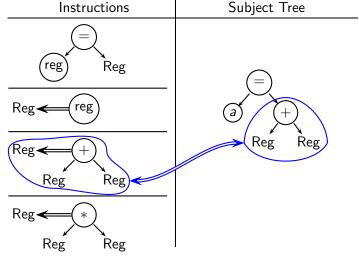

# **Tree Tiling**

Instructions are viewed as composable rules

| Instructions | Subject Tree |

|--------------|--------------|

| reg          |              |

| Reg          |              |

| Reg + Reg    |              |

| Reg * Reg    |              |

#### Tree Tiling

#### Tree Tiling

#### Tree Tiling

#### Tree Tiling

# Tree Tiling

Instructions are viewed as composable rules

#### Tree Tiling

### Tree Tiling

Instructions are viewed as composable rules

#### Tree Tiling

July 2010

27/27

Advanced MD Issues: Improving MD and Instruction Selection

Improving Machine Descriptions and Instruction Selection

Current Status:

- Preliminary investigations seem very promising

- Fewer rules

- Simple rules

July 2010

Advanced MD Issues: Improving MD and Instruction Selection

#### Current Status:

- Preliminary investigations seem very promising

- Fewer rules

- Simple rules

- Prototype of new code generator generator (cgg) is being tested in a toy compiler set up