#### Workshop on Essential Abstractions in GCC

## More Details of Machine Descriptions

GCC Resource Center

(www.cse.iitb.ac.in/grc)

Department of Computer Science and Engineering, Indian Institute of Technology, Bombay

2 July 2011

2 July 2011 MD Details: Outline 1/36 2 July 2011

MD Details: Outline

**Outline**

**Outline**

- Some details of MD constructs

- ▶ On names of patterns in .md files

- ► On the role of define\_expand

- ▶ On the role of predicates and constraints

- ► Mode and code iterators

- Defining attributes

- Other constructs

- Improving machine descriptions and instruction selection

- ► New constructs to factor out redundancy

- Cost based tree tiling for instruction selection

1/36

# More Features

Notes

2 July 2011 MD Details: More Features 2/36

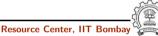

Pattern Names in .md File

2 July 2011

MD Details: More Features

Pattern Names in .md File

Notes

2/36

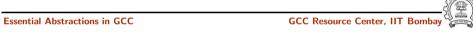

#### MD Details: More Features Role of define\_expand

**Essential Abstractions in GCC**

GCC Resource Center, IIT Bomba

2 July 2011

MD Details: More Features

4/36

#### Using define\_expand for Generating RTL statements

**Essential Abstractions in GCC**

GCC Resource Center, IIT Boml

2 July 2011

MD Details: More Features

4/36

Using define\_expand for Generating RTL statements

#### MD Details: More Features Use of Predicates

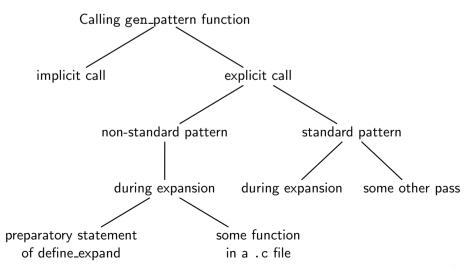

Predicates are using for matching operands

- For constructing an insn during expansion <name> must be a standard pattern name

- For recognizing an instruction (in subsequent RTL passes including pattern matching)

**Essential Abstractions in GCC**

2 July 2011

MD Details: More Features

6/36

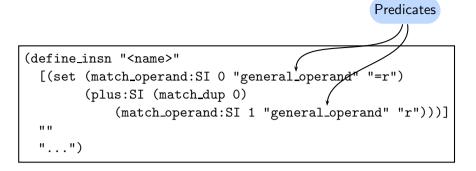

### **Understanding Constraints**

```

Constraints

(define_insn "<name>"

[(set (match_operand:SI 0 "general_operand" "=r")

(plus:SI (match_dup 0)

(match_operand:SI 1 "general_operand" "r")))]

11 11

```

- Reloading operands in the most suitable register class

- Fine tuning within the set of operands allowed by the predicate

- If omitted, operands will depend only on the predicates

## 2 July 2011

**Essential Abstractions in GCC**

GCC Resource Center, IIT

GCC Resource Center, IIT

6/36

2 July 2011

MD Details: More Features

**Understanding Constraints**

#### Role of Constraints

Consider the following two instruction patterns:

- ▶ During expansion, the destination and left operands must match the same predicate

- During recognition, the destination and left operands must be identical

**Essential Abstractions in GCC**

GCC Resource Center, IIT Bombay

2 July 2011

MD Details: More Features

8/36

#### Role of Constraints

• Consider an insn for recognition

```

(insn n prev next

(set (reg:SI 3)

(plus:SI (reg:SI 6) (reg:SI 109)))

...)}

```

- Predicates of the first pattern do not match (because they require identical operands during recognition)

- $\bullet$  Constraints do not match for operand 1 of the second pattern

- Reload pass generates additional insn to that the first pattern can be used

**Role of Constraints**

Notes

Essential Abstractions in GCC

GCC Resource Center, IIT Bombay

8/36

2 July 2011

MD Details: More Features

**Role of Constraints**

#### Part 2

# Factoring Out Common Information

Notes

2 July 2011

2 July 2011

MD Details: Factoring Out Common Information

9/36

MD Details: Factoring Out Common Information

9/36

#### **Handling Mode Differences**

#### **Handling Mode Differences**

#### Mode Iterators: Abstracting Out Mode Differences

```

(define_mode_iterator GPR [SI (DI "TARGET_64BIT")])

(define_mode_attr d [(SI "")(DI "d")])

(define_insn "sub<mode>3"

[(set (match_operand:GPR 0 "register_operand" "=d")

(minus:GPR (match_operand:GPR 1 "register_operand" "d")

(match_operand:GPR 2 "register_operand" "d")))]

" "

"<d>subu\t %0,%1,%2"

[(set_attr "type" "arith")

(set_attr "mode" "<MODE>")])

```

**Essential Abstractions in GCC**

**Essential Abstractions in GCC**

11/36

2 July 2011

MD Details: Factoring Out Common Information

#### **Handling Code Differences**

```

(define_expand "bunordered"

[(set (pc) (if_then_else (unordered:CC (cc0) (const_int 0))

(label_ref (match_operand 0 ""))

(pc)))]

{ mips_expand_conditional_branch (operands, UNORDERED);

DONE;

})

(define_expand "bordered"

[(set (pc) (if_then_else (ordered:CC (cc0) (const_int 0))

(label_ref (match_operand 0 ""))

(pc)))]

{ mips_expand_conditional_branch (operands, ORDERED);

DONE;

})

```

Mode Iterators: Abstracting Out Mode Differences

2 July 2011

**Essential Abstractions in GCC**

GCC Resource Center, IIT

2 July 2011

MD Details: Factoring Out Common Information

11/36

#### **Handling Code Differences**

#### Code Iterators: Abstracting Out Code Differences

-{(**P**)}

**Essential Abstractions in GCC**

CC Resource Center, IIT Bombay

Part 3

Miscellaneous Features

Note

**Essential Abstractions in GCC**

GCC Resource Center, IIT Bombay

# MD Details: Miscellaneous Features Defining Attributes

- Classifications are need based

- Useful to GCC phases e.g. pipelining

Property: Pipelining

Need: To classify target instructions

Construct: define\_attr

```

;; Instruction type.

(define_attr "type"

"other,multi, alu,alu1,negnot, ... str,cld, ..."

(const_string "other")

Fields:

Attribute name, all possible values, one of the possible values, default.

```

**Essential Abstractions in GCC**

GCC Resource Center, IIT Bomba

2 July 2011

MD Details: Miscellaneous Features

14/36

#### **Specifying Instruction Attributes**

- Optional field of a define\_insn

- For an i386, we choose to mark string instructions with the attribute value str

```

(define_insn "*strmovdi_rex_1"

[(set (mem:DI (match_operand:DI 2 ...)]

"TARGET_64BIT && (TARGET_SINGLE_ ...)"

"movsq"

[ (set_attr "type" "str")

...

(set_attr "memory" "both")])

```

#### NOTE

An instruction may have more than one attribute!

#### **Defining Attributes**

Notes

Essential Abstractions in GCC

GCC Resource Center, IIT Bombay

GCC Resource Center, IIT

2 July 2011

MD Details: Miscellaneous Features

14/36

#### **Specifying Instruction Attributes**

Votes

15/36

#### **Using Attributes**

(define\_insn\_reservation "pent\_str" 12 (and (eq\_attr "cpu" "pentium") (eq\_attr "type" "str") ) "pentium-np\*12")

Pipeline specification requires the CPU type to be "pentium" and the instruction type to be "str"

**Essential Abstractions in GCC**

2 July 2011

MD Details: Miscellaneous Features

16/36

MD Details: Miscellaneous Features Some Other RTL Constructs 16/36

- define\_split: Split complex insn into simpler ones e.g. for better use of delay slots

- define\_insn\_and\_split: A combination of define\_insn and define\_split Used when the split pattern matches and insn exactly.

- define\_peephole2: Peephole optimization over insns that substitutes insns. Run after register allocation, and before scheduling.

- define\_constants: Use literal constants in rest of the MD.

## **Using Attributes**

**Essential Abstractions in GCC**

#### Some Other RTL Constructs

2 July 2011

GCC Resource Center, IIT

#### Part 4

# Improving Machine Descriptions

Notes

2 July 2011

MD Details: Improving Machine Descriptions

17/36

MD Details: Improving Machine Descriptions

The Need for Improving Machine Descriptions

17/36

#### The Need for Improving Machine Descriptions

#### The Problems:

- The specification mechanism for Machine descriptions is quite adhoc

- ▶ Only syntax borrowed from LISP, neither semantics not spirit!

- ► Non-composable rules

- ▶ Mode and code iterator mechanisms are insufficient

- Adhoc design decisions

- ► Honouring operand constraints delayed to global register allocation During GIMPLE to RTL translation, a lot of C code is required

- ► Choice of insertion of NOPs

# Notes

2 July 2011

#### Handing Constraints

- define\_insns patterns have operand predicates and constraints

- While generating an RTL insn from GIMPLE, only the predicates are checked. The constraints are completely ignored

- An insn which is generated in the expander is modified in the reload pass to satisfy the constraints

- It may be possible to generate this final form of RTL during expansion by honouring constraints

- ► Honouring contraints earlier than the current place

- ⇒ May get rid of some C code in define\_expand

**Essential Abstractions in GCC**

GCC Resource Center, IIT Bombay

2 July 2011

MD Details: Improving Machine Descriptions

19/36

2 July 2011

MD Details: Improving Machine Descriptions

19/36

#### **Design Flaws in Machine Descriptions**

Multiple patterns with same structure

- Repetition of almost similar RTL expressions across multiple define\_insn an define\_expand patterns

- ► Some Modes, Predicates, Constraints, Boolean Condition, or RTL Expression may differ everything else may be identical

- One RTL expression may appears as a sub-expression of some other RTL expression

- Repetition of C code along with RTL expressions in these patterns.

#### **Handing Constraints**

Notes

Essential Abstractions in GCC

**Design Flaws in Machine Descriptions**

#### Redundancy in MIPS Machine Descriptions: Example 1

[(set (match\_operand: m 0 "register\_operand" " $c\theta$ ") (plus:m (match\_operand:m 1 "register\_operand" "c1")  $(match\_operand: \underline{m} \ 2 \ "p" \ "\underline{c2}")))]$

RTL Template

Structure

#### Details

| Pattern name                        | <u>m</u> | <u>p</u>         | <u>c0</u> | <u>c1</u> | <u>c2</u> |

|-------------------------------------|----------|------------------|-----------|-----------|-----------|

| define_insn<br>add <mode>3</mode>   | ANYF     | register_operand | =f        | f         | f         |

| define_expand<br>add <mode>3</mode> | GPR      | arith_operand    |           |           |           |

| define_insn<br>*add <mode>3</mode>  | GPR      | arith_operand    | =d,d      | d,d       | d,Q       |

**Essential Abstractions in GCC**

GCC Resource Center, IIT Bomba

2 July 2011

MD Details: Improving Machine Descriptions

21/36

#### Redundancy in MIPS Machine Descriptions: Example 2

[(set (match\_operand: m 0 "register\_operand" " $c\theta$ ") (mult:m (match\_operand: m 1 "register\_operand" "c1")  $[match\_operand: m \ 2 \ "register\_operand" \ "c2")))]$

RTL Template

Structure

#### Details

| Pattern name                                 | <u>m</u> | <u>c0</u> | <u>c1</u> | <u>c2</u> |

|----------------------------------------------|----------|-----------|-----------|-----------|

| define_insn *mul <mode>3</mode>              | SCALARF  | =f        | f         | f         |

| define_insn *mul <mode>3_r4300</mode>        | SCALARF  | =f        | f         | f         |

| define_insn mulv2sf3                         | V2SF     | =f        | f         | f         |

| define_expand mul <mode>3</mode>             | GPR      |           |           |           |

| define_insn mul <mode>3_mul3_loongson</mode> | GPR      | =d        | d         | d         |

| define_insn mul <mode>3_mul3</mode>          | GPR      | d,1       | d,d       | d,d       |

2 July 2011

#### Redundancy in MIPS Machine Descriptions: Example 1

**Essential Abstractions in GCC**

2 July 2011

MD Details: Improving Machine Descriptions

21/36

#### Redundancy in MIPS Machine Descriptions: Example 2

# MD Details: Improving Machine Descriptions Redundancy in MIPS Machine Descriptions: Example 3

[(set (match\_operand: $\underline{m}$  0 "register\_operand" " $\underline{c}\underline{0}$ ") (plus: $\underline{m}$  (mult: $\underline{m}$  (match\_operand: $\underline{m}$  1 "register\_operand" " $\underline{c}\underline{1}$ ") (match\_operand: $\underline{m}$  2 "register\_operand" " $\underline{c}\underline{2}$ ")))] (match\_operand: $\underline{m}$  3 "register\_operand" " $\underline{c}\underline{3}$ ")))]

RTL Template

Details

Structure

| Pattern name         | <u>m</u> | <u>c0</u>     | <u>c1</u> | <u>c2</u> | <u>c3</u> |

|----------------------|----------|---------------|-----------|-----------|-----------|

| *mul_acc_si          | SI       | =1*?*?,d?     | d,d       | d,d       | 0,d       |

| *mul_acc_si_r3900    | SI       | =1*?*?,d*?,d? | d,d,d     | d,d,d     | 0,1,d     |

| *macc                | SI       | =1,d          | d,d       | d,d       | 0,1       |

| *madd4 <mode></mode> | ANYF     | =f            | f         | f         | f         |

| *madd3 <mode></mode> | ANYF     | =f            | f         | f         | 0         |

**Essential Abstractions in GCC**

GCC Resource Center, IIT Bombay

2 July 2011

MD Details: Improving Machine Descriptions

23/36

#### **Insufficient Iterator Mechanism**

- Iterators cannot be used across define\_insn, define\_expand, define\_peephole2 and other patterns

- Defining iterator attribute for each varying parameter becomes tedious

- For same set of modes and rtx codes, change in other fields of pattern makes use of iterators impossible

- Mode and code attributes cannot be defined for operator or operand number, name of the pattern etc.

- Patterns with different RTL template share attribute value vector for which iterators can not be used

#### Redundancy in MIPS Machine Descriptions: Example 3

Notes

Essential Abstractions in GCC

GCC Resource Center, IIT Bombay

2 July 2011

MD Details: Improving Machine Descriptions

23/36

Insufficient Iterator Mechanism

#### MD Details: Improving Machine Descriptions Many Similar Patterns Cannot be Combined

```

(define_expand "iordi3"

[(set (match_operand:DI 0 "nonimmediate_operand" "")

(ior:DI (match_operand:DI 1 "nonimmediate_operand" "")

(match_operand:DI 2 "x86_64_general_operand" "")))

(clobber (reg:CC FLAGS_REG))]

"TARGET_64BIT"

"ix86_expand_binary_operator (IOR, DImode, operands); DONE;")

(define_insn "*iordi_1_rex64"

[(set (match_operand:DI 0 "nonimmediate_operand" "=rm,r")

(ior:DI (match_operand:DI 1 "nonimmediate_operand" "%0,0")

(match_operand:DI 2 "x86_64_general_operand" "re,rme")))

(clobber (reg:CC FLAGS_REG))]

"TARGET_64BIT

&& ix86_binary_operator_ok (IOR, DImode, operands)"

"or{q}\t{%2, %0|%0, %2}"

[(set_attr "type" "alu")

(set_attr "mode" "DI")])

```

Essential Abstractions in GCC

2 July 2011

MD Details: Improving Machine Descriptions

25/36

#### **Measuring Redundancy in RTL Templates**

| MD File | Total number of patterns | Number of primitive trees | Number of times primitive trees are used to create composite trees |

|---------|--------------------------|---------------------------|--------------------------------------------------------------------|

| i386.md | 1303                     | 349                       | 4308                                                               |

| arm.md  | 534                      | 232                       | 1369                                                               |

| mips.md | 337                      | 147                       | 921                                                                |

#### Many Similar Patterns Cannot be Combined

Essential Abstractions in GCC

2 July 2011

MD Details: Improving Machine Descriptions

25/36

#### **Measuring Redundancy in RTL Templates**

**Essential Abstractions in GCC**

#### MD Details: Improving Machine Descriptions specRTL: Key Observations

• Davidson Fraser insight

Register transfers are target specific but their form is target independent

- GCC's approach

- ▶ Use Target independent RTL for machine specification

- ► Generate expander and recognizer by reading machine descriptions

Main problems with GCC's Approach

Although the shapes of RTL statements are target independent, they have to be provided in RTL templates

• Our key idea:

Separate shapes of RTL statements from the target specific details

**Essential Abstractions in GCC**

2 July 2011

MD Details: Improving Machine Descriptions

27/36

#### Specification Goals of specRTL

Support all of the following

- Separation of shapes from target specific details

- Creation of new shapes by composing shapes

- Associtiating concrete details with shapes

- Overriding concrete details

**Essential Abstractions in GCC**

GCC Resource Center, IIT

MD Details: Improving Machine Descriptions

27/36

Specification Goals of specRTL

2 July 2011

28/36

#### Software Engineering Goals of specRTL

- Allow non-disruptive migration for existing machine descriptions

- Incremental changes

- No need to change GCC source until we are sure of the new specification

GCC must remain usable after each small change made in the machine descriptions

Essential Abstractions in GCC

GCC Resource Center, III Bombay

2 July 2011

MD Details: Improving Machine Descriptions

29/36

## Meeting the Specification Goals: Key Idea

- Separation of shapes from target specific details:

- ▶ Shape  $\equiv$  tree structure of RTL templates

- ▶ Details ≡ attributes of tree nodes (eg. modes, predicates, constraints etc.)

- Abstract patterns and Concrete patterns

- ► Abstract patterns are shapes with "holes" in them that represent missing information

- ► Concrete patterns are shapes in which all holes are plugged in using target specific information

- Abstract patterns capture shapes which can be concretized by providing details

Notes

**Essential Abstractions in GCC**

GCC Resource Center, IIT Bombay `

29/36

2 July 2011

MD Details: Improving Machine Descriptions

Meeting the Specification Goals: Key Idea

Meeting the Specification Goals: Operations

## Meeting the Specification Goals: Operations

- Creating new shapes by composing shapes: extends

- Associtiating concrete details with shapes: instantiates

- Overriding concrete details: overrides

**Essential Abstractions in GCC**

GCC Resource Center, IIT Bombay

2 July 2011

GCC Resource Center, IIT Bombay

2 July 2011

MD Details: Improving Machine Descriptions

31/36

#### **Creating Abstract Patterns**

| <pre>abstract set_plus extends set {   root.2 = plus; }</pre>              | root.1 + root.2 root.2.2                           |

|----------------------------------------------------------------------------|----------------------------------------------------|

| <pre>abstract set_macc extends     set_plus {     root.2.2 = mult; }</pre> | root.2.1 * root.2.2 root.2.2 root.2.2.1 root.2.2.2 |

Notes

**Essential Abstractions in GCC**

31/36

MD Details: Improving Machine Descriptions

Creating Abstract Patterns

#### **Creating Concrete Patterns**

```

abstract set_plus extends set

root

root.2

root.1

root.2 = plus;

root.2.

root.2.2

concrete add<mode>3.insn instantiates set_plus

{ set_plus(register_operand:ANYF:"=f",

register_operand:ANYF:"f",

register_operand:ANYF:"f");

root.2.mode = ANYF;

concrete add<mode>3.expand instantiates set_plus

{ set_plus(register_operand:GPR:"",

register_operand:GPR:"",

arith_operand:GPR:"");

root.2.mode = GPR;

```

**Essential Abstractions in GCC**

GCC Resource Center, IIT Bombay

2 July 2011

MD Details: Improving Machine Descriptions

33/36

#### **Generating Conventional Machine Descriptions**

```

abstract set_plus extends set

root

+) root.2

root.1

root.2 = plus;

root.2.2

concrete add<mode>3.insn instantiates set_plus

set_plus(register_operand:ANYF:"=f", register_operand:ANYF:"f",

register_operand:ANYF:"f");

root.2.mode = ANYF;

{: /* Conventional Machine Description Fragments */ :`

Resulting MD Specification

(define_insn "add<mode>3"

[(set (match_operand:ANYF 0 "register_operand" "=f")

(plus:ANYF (match_operand:ANYF 1 "register_operand" "f")

(match_operand:ANYF 2 "register_operand" "f")))]

/* Conventional Machine Description Fragments */

```

#### **Creating Concrete Patterns**

**Essential Abstractions in GCC**

2 July 2011

MD Details: Improving Machine Descriptions

33/36

#### **Generating Conventional Machine Descriptions**

#### **Overriding Details**

```

abstract set_plus extends set

root

+) root.2

root.2 = plus;

root.2

root.2.2

concrete add<mode>3.expand instantiates set_plus

set_plus(register_operand:GPR:"",

register_operand:GPR:"",

arith_operand:GPR:"");

root.2.mode = GPR;

concrete *add<mode>3.insn overrides add<mode>3.expand

allconstraints = ("=d,d", "d,d", "d,Q"); }

```

Essential Abstractions in GCC

2 July 2011

MD Details: Improving Machine Descriptions

35/36

#### **Current Status and Plans for Future Work**

- specRTL parser has been augmented with semantic checks Emitting conventional machine descriptions is pending

- i386 move instructions and spim add instructions have been rewritten

- Other instructions are being rewritten

- Suggestions have been received to improve the syntax

#### **Overriding Details**

**Essential Abstractions in GCC**

GCC Resource Center, IIT

2 July 2011

MD Details: Improving Machine Descriptions

35/36

**Current Status and Plans for Future Work**

**Conclusions**

#### **Conclusions**

- Separating shapes from concrete details is very helpful

- It may be possible to identify a large number of common shapes

- Machine descriptions may become much smaller Only the concrete details need to be specified

- Non-disruptive and incremental migration to new machine descriptions

- GCC source need not change until these machine descriptions have been found useful