### Workshop on Essential Abstractions in GCC

## Incremental Machine Descriptions for Spim: Levels 2, 3, and 4

GCC Resource Center (www.cse.iitb.ac.in/grc)

Department of Computer Science and Engineering, Indian Institute of Technology, Bombay

2 July 2011

Spim MD Levels 2,3,4: Outline

• Constructs supported in level 2

2 July 2011

- Constructs supported in level 3

- Constructs supported in level 4

### Part 1

# Constructs Supported in Level 2

| Operation                       | Primitive<br>Variants       | Implementation | Remark  | ì |

|---------------------------------|-----------------------------|----------------|---------|---|

|                                 | variants                    |                |         |   |

| $Dest \leftarrow Src_1 - Src_2$ | $R_i \leftarrow R_j - R_k$  | sub ri, rj, rk |         | ı |

| $Dest \leftarrow -Src$          | $R_i \leftarrow -R_j$       | neg ri, rj     |         | ì |

| $Dest \leftarrow Src_1/Src_2$   | $R_i \leftarrow R_j/R_k$    | div rj, rk     | level 2 | ì |

|                                 |                             | mflo ri        |         | ì |

| $Dest \leftarrow Src_1\%Src_2$  | $R_i \leftarrow R_j \% R_k$ | rem ri, rj, rk |         | ì |

| $Dest \leftarrow Src_1 * Src_2$ | $R_i \leftarrow R_i * R_k$  | mul ri, rj, rk |         | i |

| Operation                       | Primitive                   | Implementation | Remark  |

|---------------------------------|-----------------------------|----------------|---------|

|                                 | Variants                    |                |         |

| $Dest \leftarrow Src_1 - Src_2$ | $R_i \leftarrow R_j - R_k$  | sub ri, rj, rk |         |

| $Dest \leftarrow -Src$          | $R_i \leftarrow -R_j$       | neg ri, rj     |         |

| $Dest \leftarrow Src_1/Src_2$   | $R_i \leftarrow R_j/R_k$    | div rj, rk     | level 2 |

|                                 |                             | mflo ri        |         |

| $Dest \leftarrow Src_1\%Src_2$  | $R_i \leftarrow R_j \% R_k$ | rem ri, rj, rk |         |

| $Dest \leftarrow Src_1 * Src_2$ | $R_i \leftarrow R_i * R_k$  | mul ri, rj, rk |         |

## Bitwise Operations Required in Level 2

| Operation                                | Primitive                      | implementation  | Remark  |

|------------------------------------------|--------------------------------|-----------------|---------|

|                                          | Variants                       |                 |         |

| $Dest \leftarrow Src_1 \ll Src_2$        | $R_i \leftarrow R_j \ll R_k$   | sllv ri, rj, rk |         |

|                                          | $R_i \leftarrow R_j \ll C_5$   | sll ri, rj, c   |         |

| $Dest \leftarrow Src_1 \gg Src_2$        | $R_i \leftarrow R_j \gg R_k$   | srav ri, rj, rk |         |

|                                          | $R_i \leftarrow R_j \gg C_5$   | sra ri, rj, c   |         |

| $Dest \leftarrow Src_1\&Src_2$           | $R_i \leftarrow R_j \& R_k$    | and ri, rj, rk  |         |

|                                          | $R_i \leftarrow R_j \& C$      | andi ri, rj, c  | level 2 |

| $Dest \leftarrow Src_1 Src_2$            | $R_i \leftarrow R_j   R_k$     | or ri, rj, rk   |         |

|                                          | $R_i \leftarrow R_j   C$       | ori ri, rj, c   |         |

| $Dest \leftarrow Src_1 \ \hat{\ } Src_2$ | $R_i \leftarrow R_j \hat{R}_k$ | xor ri, rj, rk  |         |

|                                          | $R_i \leftarrow R_j \hat{C}$   | xori ri, rj, c  |         |

| $Dest \leftarrow \sim Src$               | $R_i \leftarrow \sim R_j$      | not ri, rj      |         |

For division, the spim architecture imposes use of multiple asm instructions for single operation.

4/24

# Divide Operation in spim2.md using define\_insn

- For division, the spim architecture imposes use of multiple asm instructions for single operation.

- Two ASM instructions are emitted using single RTL pattern

## rtavantages/ Bisaavantages of asing define\_insi

Spim MD Levels 2,3,4: Constructs Supported in Level 2

- Very simple to add the pattern

- Primitive target feature represented as single insn pattern in .md

- Unnecessary atomic grouping of instructions

- May hamper optimizations in general, and instruction scheduling, in particluar

# Divide Operation in spim2.md using define\_expand

• The RTL pattern can be expanded into two different RTLs.

```

(define_expand "divsi3"

[(parallel[(set (match_operand:SI 0 "register_operand" "")

(div:SI (match_operand:SI 1 "register_operand" "")

(match_operand:SI 2 "register_operand" ""))

(clobber (reg:SI 26))

(clobber (reg:SI 27))])]

emit_insn(gen_IITB_divide(gen_rtx_REG(SImode, 26),

operands[1], operands[2]));

emit_insn(gen_IITB_move_from_lo(operands[0],

gen_rtx_REG(SImode, 26)));

DONE;

```

(define\_insn "IITB\_divide"

2 July 2011

7/24

Divide pattern equivalent to div instruction in architecture.

```

[(parallel[(set (match_operand:SI 0 "LO_register_operand" "=q")

(div:SI (match_operand:SI 1 "register_operand" "r")

(match_operand:SI 2 "register_operand" "r"))

(clobber (reg:SI 27))])]

"div t%1, %2"

```

GCC Resource Center, IIT Bomba

2 July 2011

7/24

Divide pattern equivalent to div instruction in architecture.

```

[(parallel[(set (match_operand:SI 0 "LO_register_operand" "=q")

(div:SI (match_operand:SI 1 "register_operand" "r")

(match_operand:SI 2 "register_operand" "r"))

(clobber (reg:SI 27))])]

"div t%1, %2"

```

(define\_insn "IITB\_divide"

```

[(set (match_operand:SI 0 "register_operand" "=r")

(match_operand:SI 1 "LO_register_operand" "q"))]

11 11

"mflo \\t%0"

(define_insn "IITB_move_to_lo"

[(set (match_operand:SI 0 "LO_register_operand" "=q")

(match_operand:SI 1 "register_operand" "r"))]

11 11

"mtlo \\t%1"

```

(define\_insn "modsi3"

2 July 2011

• Divide pattern equivalent to div instruction in architecture.

Divide pattern equivalent to div instruction in architecture.

Spim MD Levels 2,3,4: Constructs Supported in Level 2

Advantages / Disadvantages of Using define\_expand for

- Two instructions are seperated out at GIMPLE to RTL conversion phase

- Both instructions can undergo all RTL optimizations independently

- C interface is needed in md

- Compilation becomes slower and requires more space

10/24

2 July 2011

2 July 2011

```

(match_operand:SI 2 "register_operand" ""))

(clobber (reg:SI 26))

(clobber (reg:SI 27))])]

11 11

[(parallel [(set (match_dup 3)

(div:SI (match_dup 1)

(match_dup 2)))

(clobber (reg:SI 27))])

(set (match_dup 0)

(match_dup 3))

"operands[3]=gen_rtx_REG(SImode, 26); "

```

2 July 2011

```

[(parallel [(set (match_operand:SI 0 "register_operand" "")

(div:SI (match_operand:SI 1 "register_operand" "")

(match_operand:SI 2 "register_operand" ""))

(clobber (reg:SI 26))

(clobber (reg:SI 27))])]

11 11

[(parallel [(set (match_dup 3)

[(parallel[

(set (match_operand:SI 0 "LO_register_operand" "=q")

(div:SI (match_dup 1)

(div:SI (match_operand:SI 1 "register_operand"

(match_operand:SI 2 "register_operand" "r")))

(match_dup 2)))

(clobber (reg:SI 27))])]

(clobber (reg:SI 27))])

(set (match_dup 0)

(match_dup 3))

```

"operands[3]=gen\_rtx\_REG(SImode, 26); "

2 July 2011

#

Spim MD Levels 2,3,4: Constructs Supported in Level 2

"operands[3]=gen\_rtx\_REG(SImode, 26); "

### Part 2

# Constructs Supported in Level 3

| Operation                              | Primitive         | Implementation         | Remark  |

|----------------------------------------|-------------------|------------------------|---------|

|                                        | Variants          |                        |         |

| $Dest \leftarrow fun(P_1, \dots, P_n)$ |                   | $lw r_i$ , [SP+c1]     |         |

|                                        |                   | sw $r_i$ , [SP]        |         |

|                                        |                   | :                      | Level 1 |

|                                        | call $L_{fun}, n$ | lw $r_i$ , [SP+c2]     |         |

|                                        |                   | sw $r_i$ , [SP-n*4]    |         |

|                                        |                   | jal L                  | New     |

|                                        |                   | $Dest \leftarrow \$v0$ | level 1 |

| $fun(P_1, P_2, \ldots, P_n)$           |                   | lw $r_i$ , [SP+c1]     |         |

|                                        |                   | sw $r_i$ , [SP]        |         |

|                                        |                   | :                      | Level 1 |

|                                        | call $L_{fun}, n$ | lw $r_i$ , [SP+c2]     |         |

|                                        |                   | sw $r_i$ , [SP-n*4]    |         |

|                                        |                   | jal L                  | New     |

|                                        |                   |                        | ~       |

Spim MD Levels 2,3,4: Constructs Supported in Level 3

(define insn "call"

2 July 2011

11

14/24

Spim MD Levels 2,3,4: Constructs Supported in Level 3

Spim MD Levels 2,3,4: Constructs Supported in Level 3

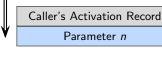

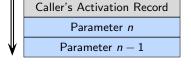

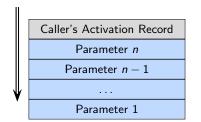

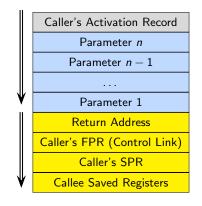

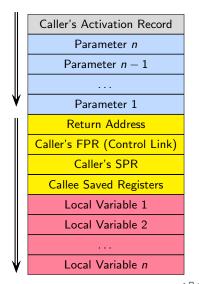

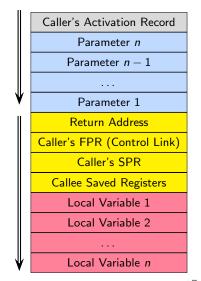

**Activation Record Generation during Call**

Operations performed by callee

Operations performed by callee

Spim MD Levels 2,3,4: Constructs Supported in Level 3

**Activation Record Generation during Call**

Caller's Activation Record

15/24

**Essential Abstractions in GCC**

GCC Resource Center, IIT Bombay

Spim MD Levels 2,3,4: Constructs Supported in Level 3

**Activation Record Generation during Call**

• Operations performed by callee

Spim MD Levels 2,3,4: Constructs Supported in Level 3

- Operations performed by caller

- Push parameters on stack.

Operations performed by callee

15/24

2 July 2011

Spim MD Levels 2,3,4: Constructs Supported in Level 3

- Operations performed by caller

- Push parameters on stack.

Parameter n Parameter n-1

Caller's Activation Record

Operations performed by callee

Operations performed by caller

2 July 2011

Push parameters on stack.

Operations performed by callee

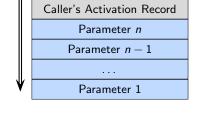

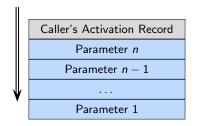

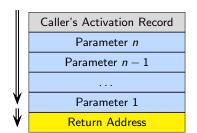

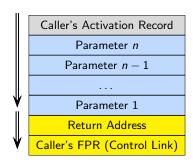

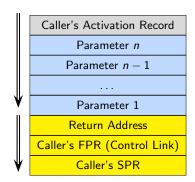

# Activation Record Generation during Call

Spim MD Levels 2,3,4: Constructs Supported in Level 3

- Operations performed by caller

- Push parameters on stack.

- Load return address in return address register.

- Operations performed by callee

- Operations performed by caller

- Push parameters on stack.

- ► Load return address in return address register.

- ► Transfer control to Callee.

- Operations performed by callee

- Operations performed by caller

- Push parameters on stack.

- Load return address in return address register.

- Transfer control to Callee.

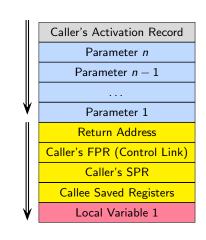

- Operations performed by callee

- Push Return address stored by caller on stack.

- Operations performed by caller

- Push parameters on stack.

- ► Load return address in return address register.

- ► Transfer control to Callee.

- Operations performed by callee

- Push Return address stored by caller on stack.

- Push caller's Frame Pointer Register.

- Operations performed by caller

- Push parameters on stack.

- Load return address in return address register.

- Transfer control to Callee.

- Operations performed by callee

- Push Return address stored by caller on stack.

- Push caller's Frame Pointer Register.

- Push caller's Stack Pointer.

- Operations performed by caller

- Push parameters on stack.

- Load return address in return address register.

- Transfer control to Callee.

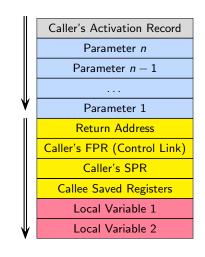

- Operations performed by callee

- Push Return address stored by caller on stack.

- Push caller's Frame Pointer Register.

- Push caller's Stack Pointer.

- Save callee saved registers, if used by callee.

- Operations performed by caller

- Push parameters on stack.

- ► Load return address in return address register.

- Transfer control to Callee.

- Operations performed by callee

- Push Return address stored by caller on stack.

- Push caller's Frame Pointer Register.

- ▶ Push caller's Stack Pointer.

- Save callee saved registers, if used by callee.

- ► Create local variables frame.

- Operations performed by caller

- Push parameters on stack.

- ► Load return address in return address register.

- ► Transfer control to Callee.

- Operations performed by callee

- Push Return address stored by caller on stack.

- Push caller's Frame Pointer Register.

- ▶ Push caller's Stack Pointer.

- Save callee saved registers, if used by callee.

- Create local variables frame.

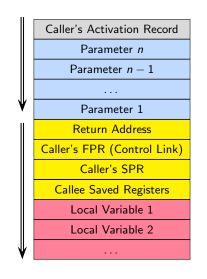

- Operations performed by caller

- Push parameters on stack.

- ► Load return address in return address register.

- ► Transfer control to Callee.

- Operations performed by callee

- Push Return address stored by caller on stack.

- Push caller's Frame Pointer Register.

- Push caller's Stack Pointer.

- Save callee saved registers, if used by callee.

- Create local variables frame.

- Operations performed by caller

- Push parameters on stack.

- ► Load return address in return address register.

- ► Transfer control to Callee.

- Operations performed by callee

- Push Return address stored by caller on stack.

- Push caller's Frame Pointer Register.

- ► Push caller's Stack Pointer.

- Save callee saved registers, if used by callee.

- Create local variables frame.

- Operations performed by caller

- Push parameters on stack.

- Load return address in return. address register.

- Transfer control to Callee.

- Operations performed by callee

- Push Return address stored by caller on stack.

- Push caller's Frame Pointer Register.

- Push caller's Stack Pointer.

- Save callee saved registers, if used by callee.

- Create local variables frame. Start callee body execution.

Spim MD Levels 2,3,4: Constructs Supported in Level 3

16/24

2 July 2011

```

{

```

})

```

spim_prologue();

DONE;

```

Spim MD Levels 2,3,4: Constructs Supported in Level 3

11 11

₹

2 July 2011

DONE;

spim\_prologue();

```

(set (mem:SI (reg:SI $sp))

(reg:SI 31 $ra))

(set (mem:SI (plus:SI (reg:SI $sp)

(define_expand "prologue"

(const_int -4 )))

[(clobber (const_int 0))]

(reg:SI $sp))

(set (mem:SI (plus:SI (reg:SI $sp)

(const_int -8 )))

(reg:SI $fp))

(set (reg:SI $fp)

(reg:SI $sp))

(set (reg:SI $sp)

(plus:SI (reg:SI $fp)

(const_int -36)))

```

(define\_expand "epilogue" [(clobber (const\_int 0))]

spim\_epilogue();

DONE;

**Essential Abstractions in GCC**

2 July 2011

11 11

17/24

(parallel [ (return)

```

(set (reg:SI $ra)

(mem:SI (reg:SI $sp)))

```

(use (reg:SI \$ra))])

GCC Resource Center, IIT Bombay

#### Part 3

## Constructs Supported in Level 4

Implementation Remark

Operation

2 July 2011

18/24

## Operations Required in Level 4

Primitive

|                      | Variants                     |                   |  |

|----------------------|------------------------------|-------------------|--|

| $Src_1 < Src_2$ ?    |                              |                   |  |

| goto L : <i>PC</i>   | $CC \leftarrow R_i < R_i$    |                   |  |

|                      | CC < 0 ? goto L : PC         | blt $r_i, r_j, L$ |  |

| $Src_1 > Src_2$ ?    |                              | -                 |  |

| goto L : <i>PC</i>   | $CC \leftarrow R_i > R_j$    |                   |  |

|                      | CC > 0 ? goto $L : PC$       | bgt $r_i, r_j, L$ |  |

| $Src_1 \leq Src_2$ ? |                              |                   |  |

| goto L : <i>PC</i>   | $CC \leftarrow R_i \leq R_i$ |                   |  |

|                      | $CC \le 0$ ? goto L : PC     | ble $r_i, r_j, L$ |  |

| $Src_1 \geq Src_2$ ? |                              |                   |  |

| goto L : <i>PC</i>   | $CC \leftarrow R_i \geq R_j$ |                   |  |

|                      | $CC \ge 0$ ? goto L : PC     | bge $r_i, r_j, L$ |  |

## Operations Required in Level 4

| Operation            | Primitive                    | Implementation    | Remark |

|----------------------|------------------------------|-------------------|--------|

|                      | Variants                     |                   |        |

| $Src_1 == Src_2$ ?   |                              |                   |        |

| goto L : PC          | $CC \leftarrow R_i == R_j$   |                   |        |

|                      | CC == 0? goto L : PC         | beq $r_i, r_j, L$ |        |

| $Src_1 \neq Src_2$ ? |                              |                   |        |

| goto L : PC          | $CC \leftarrow R_i \neq R_j$ |                   |        |

|                      | $CC \neq 0$ ? goto L : PC    | bne $r_i, r_j, L$ |        |

(define\_insn "cbranchsi4"

20/24

char \*

2 July 2011

21/24

# conditional\_insn (enum rtx\_code code,rtx operands[])

```

{

switch(code)

₹

case EQ:return "beq %1, %2, %13";

case NE:return "bne %1, %2, %13";

case GE:return "bge %1, %2, %13";

case GT:return "bgt %1, %2, %13";

case LT:return "blt %1, %2, %13";

case LE:return "ble %1, %2, %13";

case GEU:return "bgeu %1, %2, %13";

case GTU:return "bgtu %1, %2, %13";

case LTU:return "bltu %1, %2, %13";

case LEU:return "bleu %1, %2, %13";

default: /* Error. Issue ICE */

```

2 July 2011

22/24

(define\_code\_iterator cond\_code

```

[lt ltu eq ge geu gt gtu le leu ne])

(define_expand "cmpsi"

[(set (cc0) (compare

(match_operand:SI 0 "register_operand" "")

(match_operand:SI 1 "nonmemory_operand" "")))]

11 11

compare_op0=operands[0];

compare_op1=operands[1];

DONE:

```

Spim MD Levels 2,3,4: Constructs Supported in Level 4

[(set (pc) (if\_then\_else (cond\_code:SI (match\_dup 1)

{

11 11

(define\_expand "b<code>"

(pc)))]

operands[1]=compare\_op0;

2 July 2011

```

operands[2]=compare_op1;

if(immediate_operand(operands[2],SImode))

operands[2]=force_reg(SImode,operands[2]);

GCC Resource Center, IIT Bomba

```

2 July 2011

```

(define_insn "*insn_b<code>"

[(set (pc)

(if then else

(cond_code:SI

(match_operand:SI 1 "register_operand" "r")

(match_operand:SI 2 "register_operand" "r"))

(label_ref (match_operand 0

(pc)))]

11 11

"*

return conditional_insn(<CODE>,operands);

11

```

24/24