# GCC Internals: A Conceptual View - Part II

### Abhijat Vichare

CFDVS, Indian Institute of Technology, Bombay

January 2008

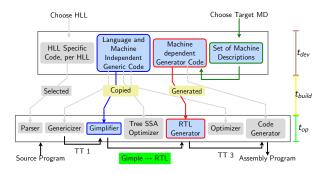

### Plan

#### Part I

- GCC: Conceptual Structure

- C Program through GCC

- Building GCC

#### Part II

- Gimple

- The MD-RTL and IR-RTL Languages in GCC

- GCC Machine Descriptions

## Part I

# Gimple

GIMPLE: Goals (2:1:

#### The Goals of GIMPLE are

- Lower control flow

Program = sequenced statements + unrestricted jump

- Simplify expressions, introduce temporary variables as needed Typically: two operand assignments!

- Simplify scope

move local scope to block begin including temporaries

### Notice

Lowered control flow  $\rightarrow$  nearer to register machines + Easier SSA!

## Gimple at $t_{dev}$ : GIMPLE code in GCC

### Tree manipulation passes $({ t tree-optimize.c})$

Gimplifier case analyzes GENERIC nodes, calls corresponding gimplifier.

```

\{Gimple\} = \{AST/Generic\} - \{Control flow nodes\}

```

- Node type specific gimplifiers

- Optimization passes on tree representation, and

- Translate to next IR, i.e. RTL

- Depth first traverse the "input" Gimple representation

- Generate a linear list RTL representation

#### But we have a problem ...

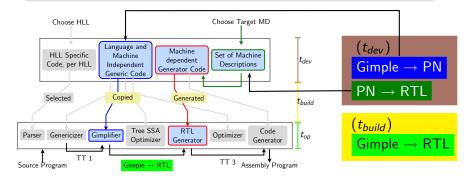

## Gimple → RTL Translation Table – Part I

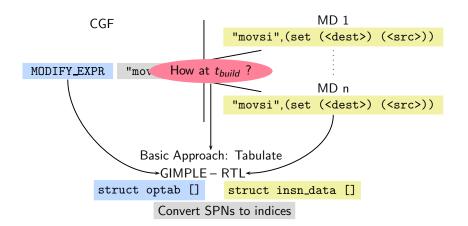

PROBLEM: Gimple  $(m/c \text{ indep.}) \rightarrow RTL (m/c \text{ specific})!$

To Do: Implement m/c indep. to m/c dep. translation at  $t_{dev}$

GIVEN: the actual target will be known only at  $t_{build}$

### Gimple → RTL Translation Table – Part I

PROBLEM: Gimple (m/c indep.)  $\rightarrow$  RTL (m/c specific)!

To Do: Implement m/c indep. to m/c dep. translation at  $t_{dev}$ GIVEN: the actual target will be known only at  $t_{build}$

(3:1:9)

MODIFY\_EXPR

(set (<dest>) (<src>))

Target indep. rep. to target dep. rep. in GCC

(3:1:9)

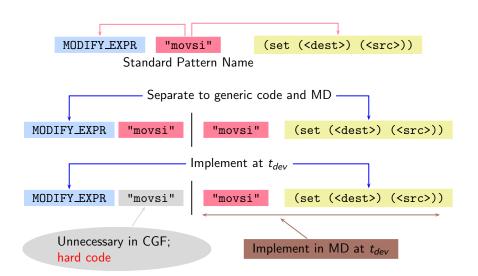

```

MODIFY_EXPR "movsi" (set (<dest>) (<src>))

Standard Pattern Name

```

3:1:9

```

MODIFY_EXPR "movsi" (set (<dest>) (<src>))

Standard Pattern Name

Separate to generic code and MD

MODIFY_EXPR "movsi" (set (<dest>) (<src>))

```

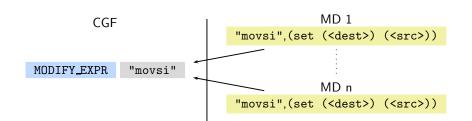

(3:1:10)

Retargetability  $\Rightarrow$  Multiple MD vs. One CGF! (3:1:10)

### Part II

The MD-RTL and IR-RTL Languages in GCC

### RTL Goals and Use

Goal 1: Specify target instruction semantics at  $t_{dev}$

Capture target instruction semantics as RTXs

Use MD constructs and operators | → The MD-RTL Language

### Goal 2: Represent input program at $t_{op}$

- Lower data

- "Express" the "captured" target semantics in IR

- Goal: Every RTX of last RTL pass = unique ASM string.

Use IR constructs and operators | → The IR-RTL Language

### Notice

Lowered data and procedures → nearer to typical hardware

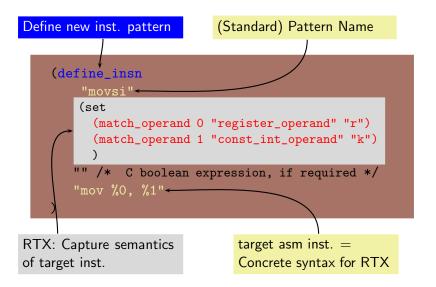

## Goal 1 Example: Specifying target inst. semantics

```

(define_insn

"movsi"

(set

(match_operand 0 "register_operand" "r")

(match_operand 1 "const_int_operand" "k")

)

"" /* C boolean expression, if required */

"mov %0, %1"

)

```

## Goal 1 Example: Specifying target inst. semantics

## Goal 1 Example: Specifying target inst. semantics

```

MD RTX

MD constructs

(define_insn

"movsi"

<del>(</del>set

(match_operand 0 "register_operand" "r")

(match_operand 1 "const_int_operand" "k")

C boolean expression, if required */

"mov %0, %1"

RTL Expression (RTX)

Operators

```

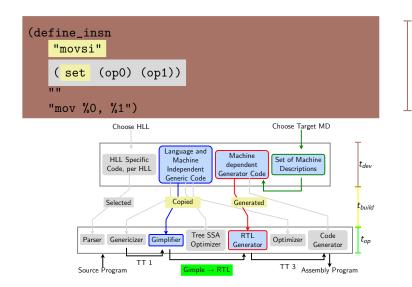

### From Goal 1 to Goal 2: RTL at t<sub>build</sub>

### Alert: At t<sub>build</sub>

Convert MD-RTL at  $t_{develop}$  to RTL data structures, and compile.

```

The Data Structure for RTL Objects (In rtl.h)

struct rtx_def { /* RTL codes (e.g. SET) enum-med

from $GCCHOME/gcc/rtl.def */

ENUM_BITFIELD(rtx_code) code : 16;

ENUM_BITFIELD(machine_mode) mode : 8;

unsigned int

jump : 1;

/* ... a few such flags */

union u {

rtunion fld[1];

HOST_WIDE_INT hwint[1];

};

```

t<sub>dev</sub>

```

(define_insn

"movsi"

(set (op0) (op1))

""

"mov %0, %1")

```

```

t<sub>dev</sub>

```

```

rtx

gen_movsi (rtx operand0, rtx operand1)

{

...

emit_insn (gen_rtx_ SET (VOIDmode, op0, op1));

...

}

```

$t_{build}$

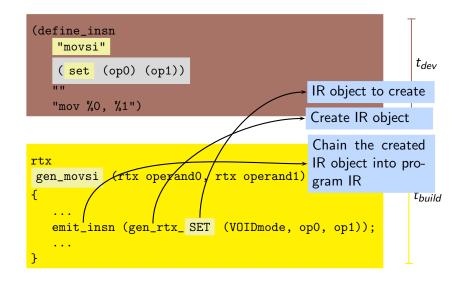

(define\_insn "movsi" (set (op0) (op1)) %1") rtx (rtx operand0, rtx operand1) gen\_movsi  $t_{build}$ emit\_insn (gen\_rtx\_ SET (VOIDmode, op0, op1)); . . .

```

(define_insn

"movsi"

(set (op0) (op1))

11 11

IR object to create

"mov %0, %1")

rtx

gen_movsi (rtx operand0 √ rtx operand1)

t_{build}

emit_insn (gen_rtx_ SET (VOIDmode, op0, op1));

. . .

```

```

(define_insn

"movsi"

(set (op0) (op1))

11 11

IR object to create

"mov %0, %1")

Create IR object

rtx

gen_movsi (rtx operand0 √ rtx operand1)

t_{build}

emit_insn (gen_rtx_ SET (VOIDmode, op0, op1));

. . .

```

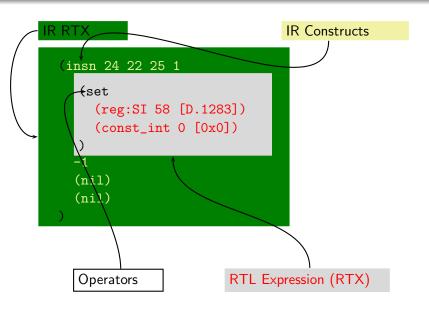

```

IR RTX 1

(insn 24 22 25 1

(set

IR RTX ...

(reg:SI 58 [D.1283])

(const_int 0 [0x0])

IR RTX 24

IR RTX ...

(nil)

(nil)

IR RTX n

```

See: RTL dump in "C Program through GCC"

```

Instruction position in sequence

Previous inst.

Next inst.

(insn 24 22 25 1

Instantiation of RTX

(set

specified in MD.

(reg:SI 58 [D.1283])

(const_int 0 [0x0])

Register #58 matches

the corresponding

match_operand spec.

(nil)

(nil)

Similarly, for the

next operand.

```

```

(insn 24 22 25 1

(set

(reg:SI 58 [D.1283])

(const_int 0 [0x0])

(nil)

(nil)

```

```

Note:

```

RTX is incomplete.

Hard register for pseudoregister #58 unknown (yet).

Allocate: #58 = eax

RTX is now complete.

Instantiated RTX is target dependent because the RTX specified in MD captures target instruction semantics.

### Part III

# GCC Machine Descriptions

## Why MD at $t_{dev}$ ?

### MDs are written in MD-RTL

### Main Purpose: Gimple $\rightarrow$ IR-RTL Translation at $t_{run}$

Gimple IR-RTL

m/c indep. m/c specific.

Known at  $t_{dev}$  Unknown at  $t_{dev}$ , known at  $t_{build}$

Single "instance" Per target "instance"

### Other Purposes

- IR-RTL Manipulations

- Gimple → IR-RTL

- IR-RTL → IR-RTL (combine or split)

- ullet IR-RTL  $\to$  Target ASM

- Support

- Programmer support through convenience constructs

- Additional heuristics for Instruction selection

### The Information in MD

- Processor instructions useful to GCC

- Processor characteristics useful to GCC

- Target ASM syntax

- IR-RTL → IR-RTL transformations (GCC code performs the transformation computations, MD supplies their target patterns)

- Target Specific Optimizations

## Syntactic Entities in GCC MD

#### Two kinds:

- Necessary Specifications

- Processor instructions useful to GCC

- ullet One Gimple o One IR-RTL

- $\bullet$  One Gimple  $\to$  More than one IR-RTL

- Processor characteristics useful to GCC

- Target ASM syntax

- $\bullet \ \mathsf{IR}\text{-}\mathsf{RTL} \to \mathsf{IR}\text{-}\mathsf{RTL} \ \mathsf{transformations}$

- Target Specific Optimizations

- Programming Conveniences

- define\_insn\_and\_split

- define\_constants

- define\_cond\_exec

- define\_automaton

define\_insn

define\_expand

define\_cpu\_unit

part of define\_insn

define\_split

define\_peephole2

Tip

See: \$GCCHOME/gcc/rtl.def.

## Reading a GCC MD

#### Focus on the RTX!

- Target semantics are in the RTX!

- Target ASM syntax is one argument of define\_insn

- The set of define\_insns must be "complete".

- All IR-RTL manipulations must have a define\_insn.

### Example

```

(define_insn "trap" ; "trap" pattern in i386.md

[(trap_if (const_int 1) (const_int 5))]

"" "int $5")

(define_insn "trap" ; "trap" pattern in mips.md

[(trap_if (const_int 1) (const_int 0))]

"" "break 0") ; some target asm details ignored

```