Workshop on Essential Abstractions in GCC

## Introduction to Machine Descriptions

GCC Resource Center (www.cse.iitb.ac.in/grc)

Department of Computer Science and Engineering, Indian Institute of Technology, Bombay

2 July 2012

MD Intro: Outline

Outline

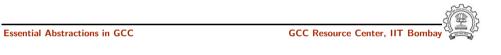

- Influences on GCC Machine Descriptions

- Organization of GCC Machine Descriptions

- Machine description constructs

- The essence of retargetability in GCC

### Examples of Influences on the Machine Descriptions

Part 1

Influences on Machine Descriptions

#### **GCC** Machine Descriptions

Part 2

# Organization of GCC MD

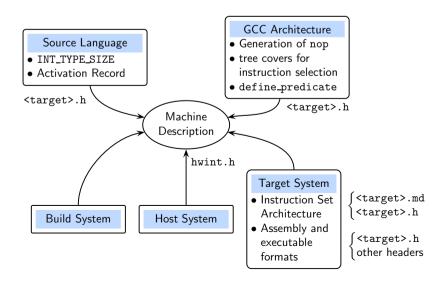

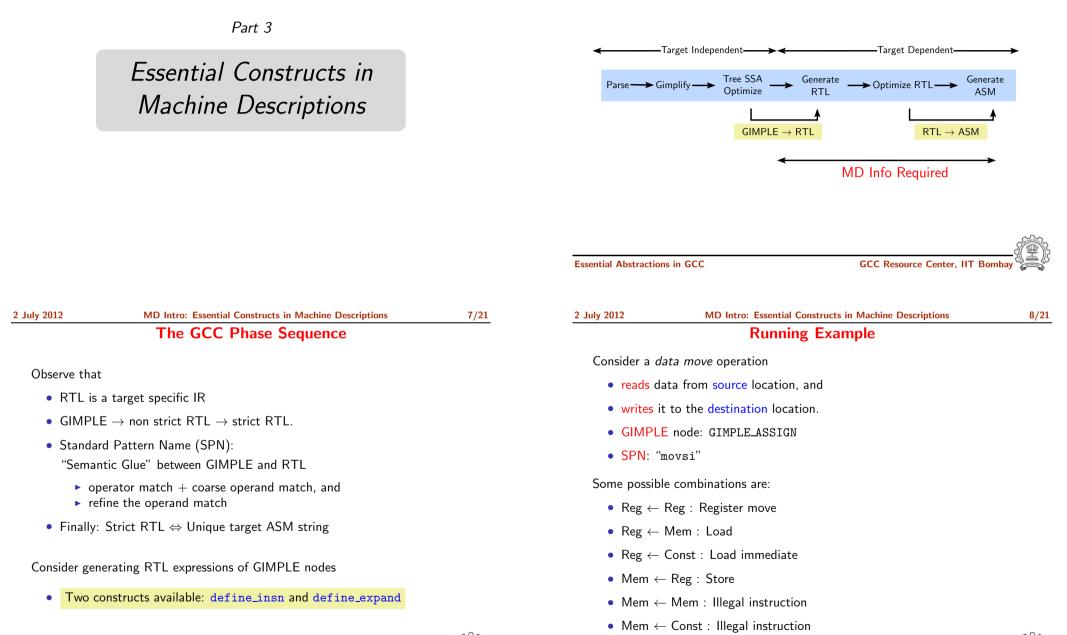

- Processor instructions useful to GCC

- Processor characteristics useful to GCC

- Target ASM syntax

- Target specific optimizations as IR-RTL → IR-RTL transformations (GCC code performs the transformation computations, MD supplies their *target patterns*)

- Peephole optimizations

- Transformations for enabling scheduling

**Essential Abstractions in GCC**

2 July 2012

| The define_expand Construct     Relationship Between <target>.md, <tar<br><target>.h Files       (define_expand</target></tar<br></target>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | iptions 13,          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| <pre>[[set (match_operand:SI 0 "nonimmediate_operand" "")<br/>(match_operand:SI 1 "general_operand" "")<br/>)] "" { if (GET_CODE (operands[0]) == MEM &amp;&amp;<br/>GET_CODE (operands[1]) = REG)<br/>if (canc_reate_perado_p(0)<br/>operands[1] = force_reg (SImode, operands[1]);<br/>) mulal Abstractions in GCC GCC Resource Center, ITT Bombay with Abstractions in GCC GCC Resource Center, ITT Bombay with Abstractions in GCC GCC Resource Center, ITT Bombay i; Here z is the constraint character defined in<br/>;; REG_CLASS_FROM_LETTER_P ;; The register Szero is used here.<br/>(define_insn "IITB_move_zero"<br/>[(set (match_operand:SI 0 "nonimmediate_operand" "g_z")<br/>)] "" "g more \t%0,%1 sv \t%</pre> | get>.c, and          |

| <pre>(match_operand:SI 1 "general_operand" "") ) ""  (match_operand:SI 1 "general_operand" "") (match_operand:SI 1 "general_operand" "") (match_operand:SI 1 "general_operand" "Z, z") )  (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 0 "nonimediate_operand" "Z, z") ) (match_operand:SI 1 "general_operand" "Z, z") ) (match_operand:SI 1 "general_ope</pre>                                                 |                      |

| <pre> Example:  Example: Example:  Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Example: Ex</pre>                                                 |                      |

| <pre>     if (GET_CODE (operands[0]) == MEM &amp;&amp;         GET_CODE (operands[1]) != REG)         if (can_create_pseudo_p())         operands[1] = force_reg (SImode, operands[1]);     }      tial Abstractions in GCC GCC Resource Center. IIT Bombay          (attach_operand:SI o "nonimmediate_operand" "=r,m")         (match_operand:SI 0 "n</pre>                                         |                      |

| <ul> <li>if (GET_CODE (operands[0]) == MEM &amp;&amp;<br/>GET_CODE (operands[1]) != REG)<br/>if (can, create_peedo_p())<br/>operands[1] = force_reg (SImode, operands[1]);</li> <li>if (Abstractions in GCC</li> <li>GCC Resource Center, HT Bombay</li> <li>Essential Abstractions in GCC</li> <li>GCC Resource Center, HT Bombay</li> <li>Essential Abstractions in GCC</li> <li>GCC Resource Center, HT Bombay</li> <li>if (2012</li> <li>MD Intro: Essential Constructs in Machine Descriptions</li> <li>14/21</li> <li>Call Essential Constructs in Machine Descriptions</li> <li>Here z is the constraint character defined in<br/>; REG_CLASS_FROM_LETTER_P<br/>[Set (match_operand:SI 0 "nonimmediate_operand" "= r, m")<br/>(match_operand:SI 1 "zero_register_operand" "= r, m")<br/>(match_operand:SI 1 "zero_register_operand" "= r, m")</li> <li>(match_operand:SI 0 "nonimmediate_operand" "= r, m")</li> <li>(match_operand:SI 1 "zero_register_operand" "= r, m")</li></ul>                                                                                                                                          | e                    |

| <pre>if (can_create_pseudo_p())     operands[1] = force_reg (SImode, operands[1]); }  iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay iii Abstractions in GCC GCC Resource Center, IIT Bombay</pre>                                                  |                      |

| tial Abstractions in GCC       GCC Resource Center, IIT Bombay       Essential Abstractions in GCC       GCC Resource         2012       MD Intro: Essential Constructs in Machine Descriptions       14/21       2 July 2012       MD Intro: Essential Constructs in Machine Descriptions       2 July 2012       MD Intro: Essential Constructs in Machine Descriptions       2 July 2012       MD Intro: Essential Constructs in Machine Descriptions       2 July 2012       MD Intro: Essential Constructs in Machine Descriptions       2 July 2012       MD Intro: Essential Constructs in Machine Descriptions       4 Constructs in Machine Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ∙.c file             |

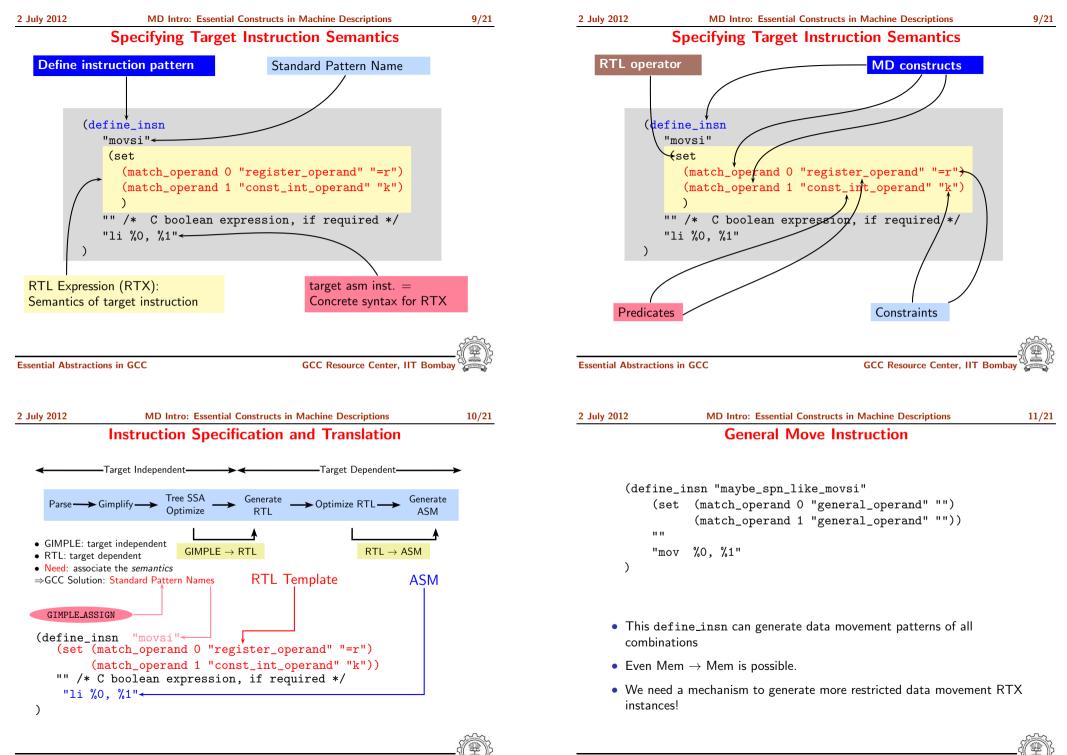

| 2012       MD Intro: Essential Constructs in Machine Descriptions       14/21         2 July 2012         MD Intro: Essential Constructs in Machine Descriptions         14/21         Register Class Constraints in <target>.md File         Register Class Constraint character defined in<br/>; REG_CLASS_FROM_LETTER_P<br/>; The register \$zero is used here.<br/>lefine_insn "IITB_move_zero"<br/>[(set<br/>(match_operand:SI 0 "nonimmediate_operand" "=r,m")<br/>(match_operand:SI 1 "zero_register_operand" "Z,z")<br/>)]<br/>""<br/>move \t%0,%1<br/>sw \t%1, %m0"       MD Intro: Essential Constructs in Machine Desc<br/>Register Class specification in <target< table="">       /* From spim.h */<br/>#define REG_CLASS_FROM_LETTER_P<br/>reg_class_from_letter<br/>enum reg_class<br/>{<br/>NO_REGS,<br/>CALLER_SAVED_REGS,<br/>CALLER_SAVED_REGS,<br/>CALLER_SAVED_REGS,<br/>ALL_REGS,<br/>LIM_REG_CLASSES<br/>};<br/>#define REG_CLASS_CONTENTS<br/>{0x00000000, 0x00000001, 0xff00ffff, 0x00ff00</target<></target>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | e Center, IIT Bombay |

| Register Class Constraints in <target>.md File       Register Class specification in <target< th="">         Register Class Specification in <target< td="">       /* From spin.h */         ; Here z is the constraint character defined in       #define REG_CLASS_FROM_LETTER_P         ; The register \$zero is used here.       reg_class_from_letter         lefine_insn "IITB_move_zero"       [(set         [(match_operand:SI 0 "nonimmediate_operand" "=r,m")       CALLER_SAVED_REGS, CALLEE_SAVED_REGS         (match_operand:SI 1 "zero_register_operand" "Z,z")       BASE_REGS, CENERAL_REGS, ALL_REGS, ALL_REGS, ALL_REGS, ALL_REGS, CONTENTS         ""       **         "@       **         move \t%0,%1       **         sw \t%1, %m0"       Ox00000000, Ox00000001, Ox0000001</target<></target<></target>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |

| <pre>; Here z is the constraint character defined in ; REG_CLASS_FROM_LETTER_P ; The register \$zero is used here. define_insn "IITB_move_zero"   [(set</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |

| <pre>; Here z is the constraint character defined in ; REG_CLASS_FROM_LETTER_P ; The register \$zero is used here. define_insn "IITB_move_zero"   [(set</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |

| <pre>; The register \$zero is used here.<br/>define_insn "IITB_move_zero"<br/>[(set</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | λ                    |

| <pre>define_insn "IITB_move_zero" {     [(set         (match_operand:SI 0 "nonimmediate_operand" "=r,m")         (match_operand:SI 1 "zero_register_operand" "z,z")         (match_operand:SI 1 "zero_register_operand" "z,z")         BASE_REGS, GENERAL_REGS,         J]         ""         "0         move \t%0,%1         sw \t%1, %m0"</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |

| <pre>[(set<br/>(match_operand:SI 0 "nonimmediate_operand" "=r,m")<br/>(match_operand:SI 1 "zero_register_operand" " Z ,z")<br/>(match_operand:SI 1 "zero_register_operand" " Z ,z")<br/>)]</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| <pre>(match_operand:SI 0 "nonimmediate_operand" "=r,m") CALLER_SAVED_REGS, CALLEE_SAVED_REGS<br/>(match_operand:SI 1 "zero_register_operand" "z,z") BASE_REGS, GENERAL_REGS,<br/>)] ALL_REGS, LIM_REG_CLASSES<br/>""<br/>"@<br/>move \t%0,%1<br/>sw \t%1, %m0" 4define REG_CLASS_CONTENTS<br/>{0x0000000, 0x0000001, 0xff00ffff, 0x00ff00</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

| (match_operand:SI 1 "zero_register_operand" " z ,z")       BASE_REGS, GENERAL_REGS, LIM_REG_CLASSES         )]       ALL_REGS, LIM_REG_CLASSES         ""       };         "0       #define REG_CLASS_CONTENTS         move \t%0,%1       #define REG_CLASS_CONTENTS         sw \t%1, %m0"       {0x00000001, 0xff00ffff, 0x00ff00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| )] ALL_REGS, LIM_REG_CLASSES<br>"" "0 move \t%0,%1 sw \t%1, %m0" ALL_REGS, LIM_REG_CLASSES "" ALL_REGS, LIM_REG_CLASSES "" "0 "0 "0 "0 "0 "0 "0 "0 "0 "0 "0 "0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |

| "" "@ move \t%0,%1 sw \t%1, %m0" }; #define REG_CLASS_CONTENTS {0x00000001, 0xff00ffff, 0x00ff00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| "@<br>move \t%0,%1 #define REG_CLASS_CONTENTS<br>sw \t%1, %m0" {0x00000001, 0xff00ffff, 0x00ff00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | \<br>\               |

| move \t%0,%1         #define REG_CLASS_CONTENTS           sw \t%1, %m0"         {0x000000001, 0xff00ffff, 0x00ff00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| sw \t%1, %m0" {0x00000000, 0x00000001, 0xff00ffff, 0x00ff00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Ο, \                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

| he Register Class letter code ————————————————————————————————————                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ass Enumeration      |

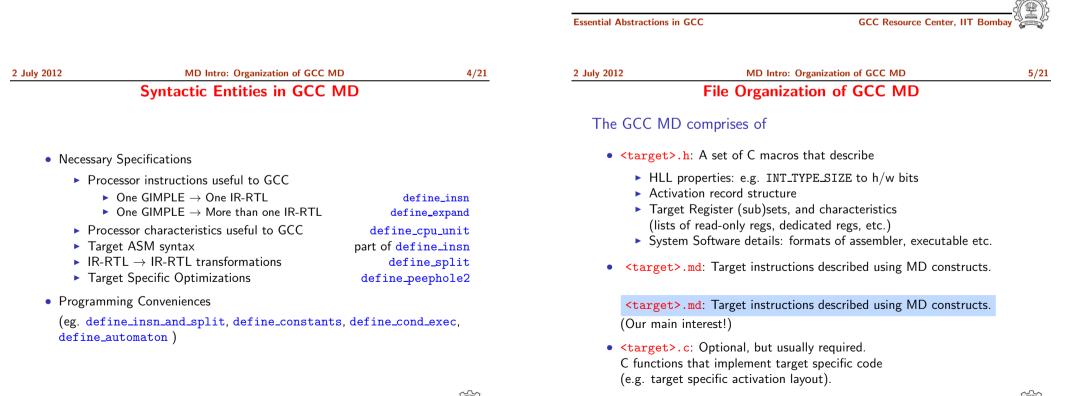

The <target>.c File

16/21

MD Intro: The Essence of Retargetability

MD Intro: The Essence of Retargetability

20/21

21/21

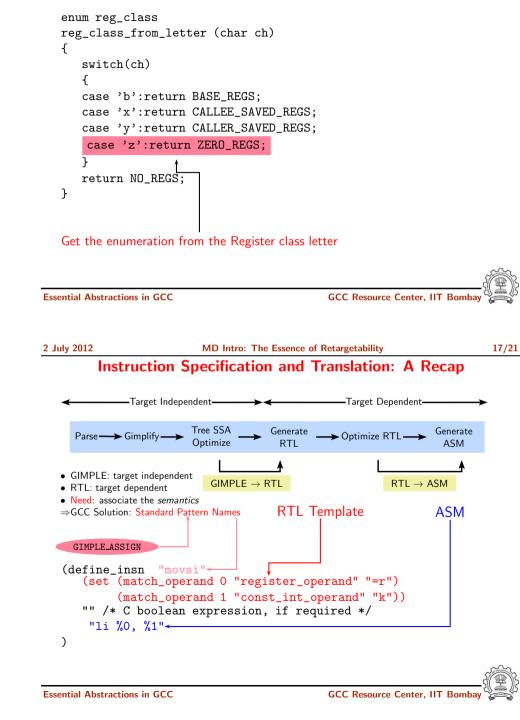

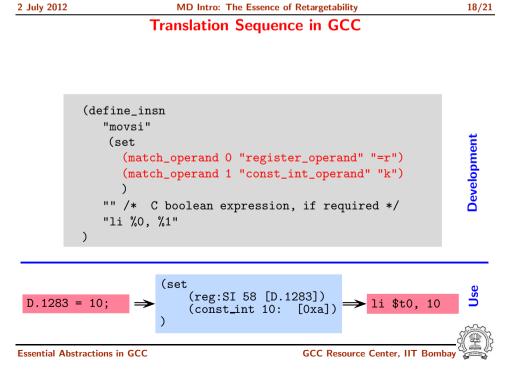

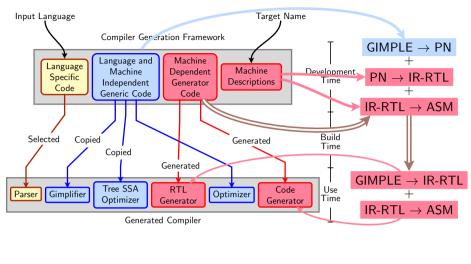

## **Retargetability Mechanism of GCC**

When are the machine descriptions read?

- During the build process

- When a program is compiled by gcc the information gleaned from machine descriptions is consulted

2 July 2012

**Essential Abstractions in GCC**

MD Intro: Summary

- GCC achieves retargetability by reading the machine descriptions and generating a back end customised to the machine descriptions

- Machine descriptions are influenced by: The HLLs, GCC architecture, and properties of target, host and build systems

- Writing machine descriptions requires: specifying the C macros, target instructions and any required support functions

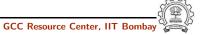

- define\_insn and define\_expand are used to convert a GIMPLE representation to RTL

Essential Abstractions in GCC

GCC Resource Center, IIT Bombay

Part 5

Summary