# CS230: Digital Logic Design and Computer Architecture Lecture 20: Cache Coherence and DRAM https://www.cse.iitb.ac.in/~biswa/courses/CS230/main.html

https://www.cse.iitb.ac.in/~biswa/

### Cache Coherence

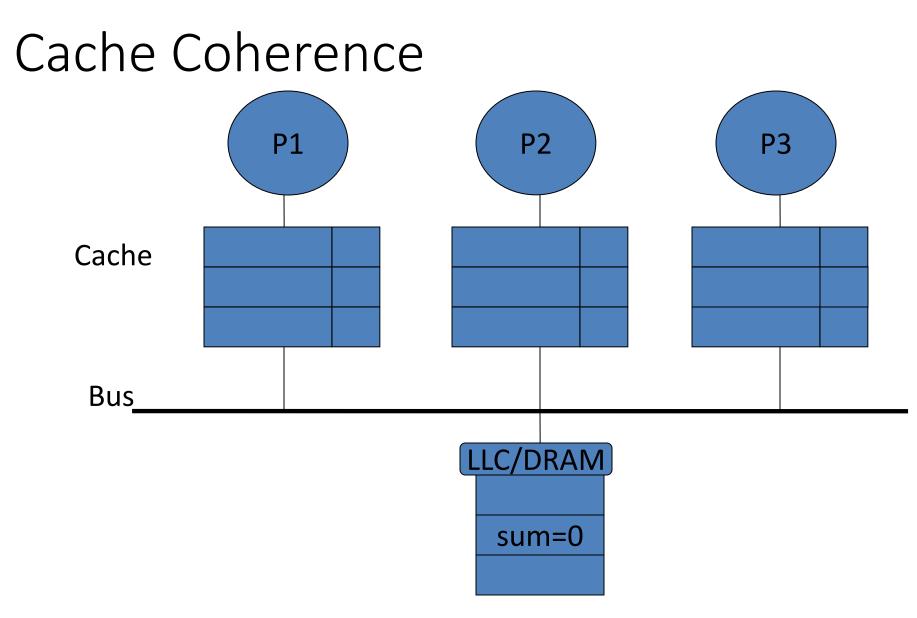

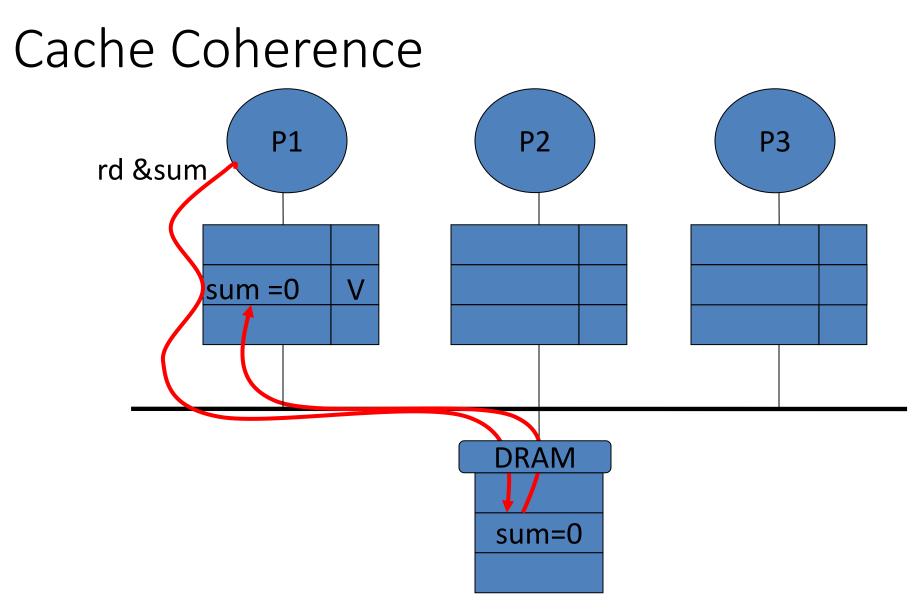

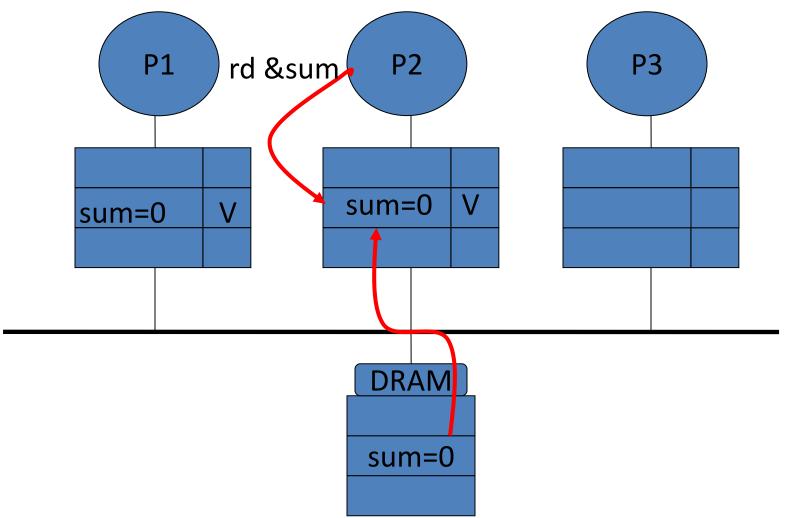

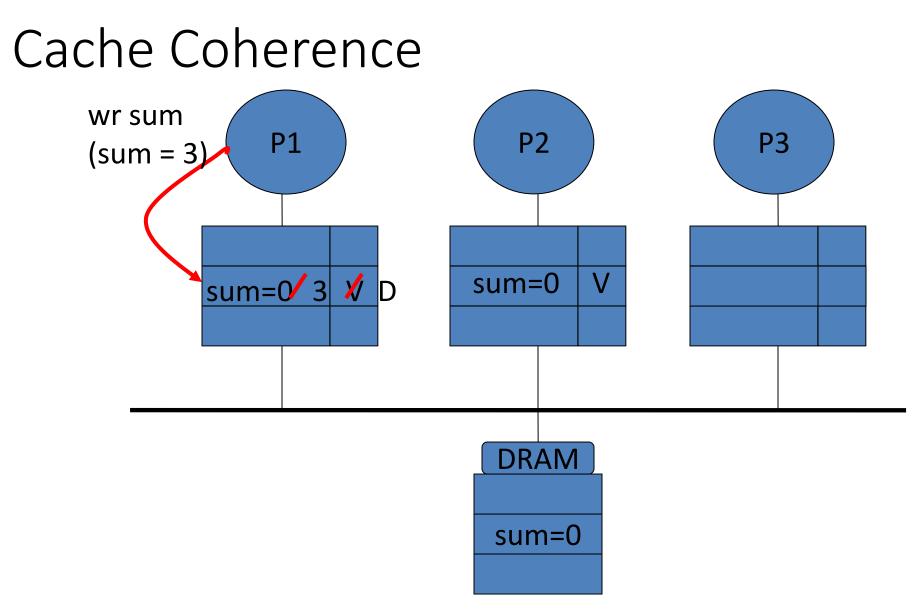

## Cache Coherence

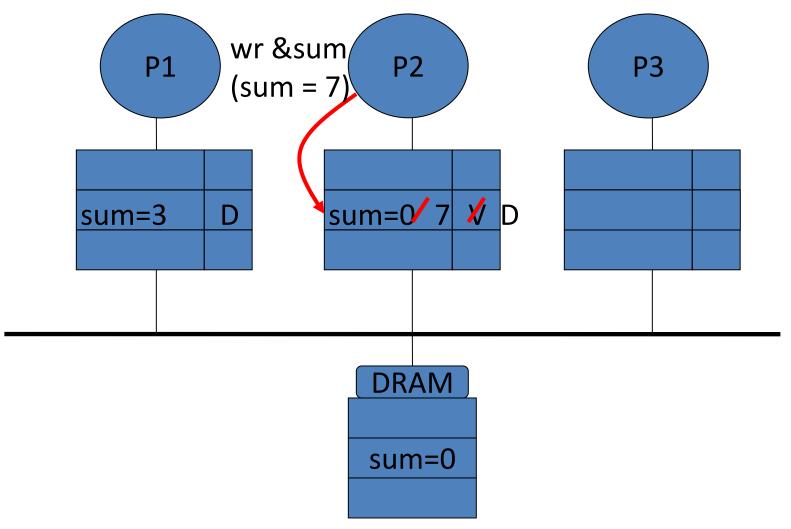

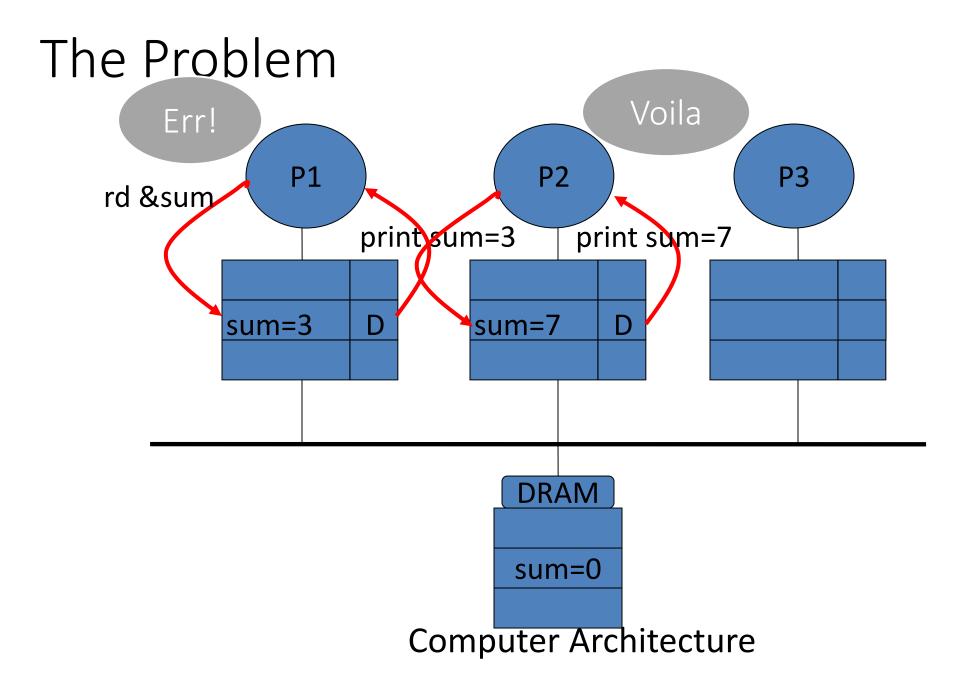

## The Problem

If multiple cores cache the same block, how do they ensure they all see a consistent state?

Solution:

1. Write Propagation: All writes eventually become visible to other cores.

2. Write Serialization: All cores see write to a cache line in same order.

Need a protocol to ensure (1) and (2) called *cache coherence protocol*

### Invalidate/Update Invalidate –

- Write to a cache line, and simultaneously broadcast invalidation of address to all others

- Other cores clear/invalidate their cache lines

### Update -

- Write to a cache line, and simultaneously broadcast written data to all others

- Other cores update their caches if data was present

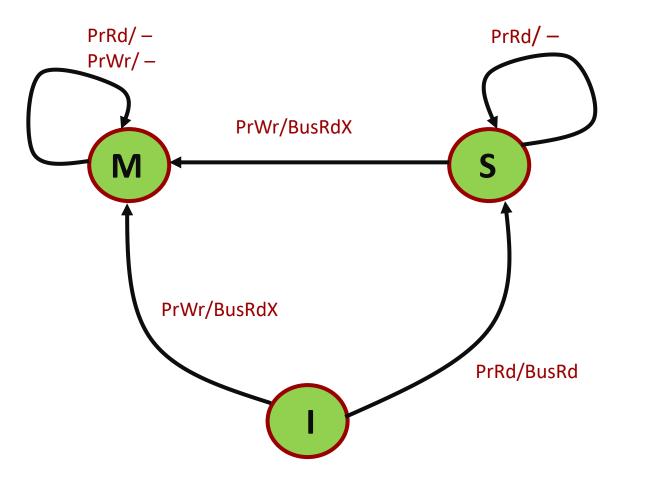

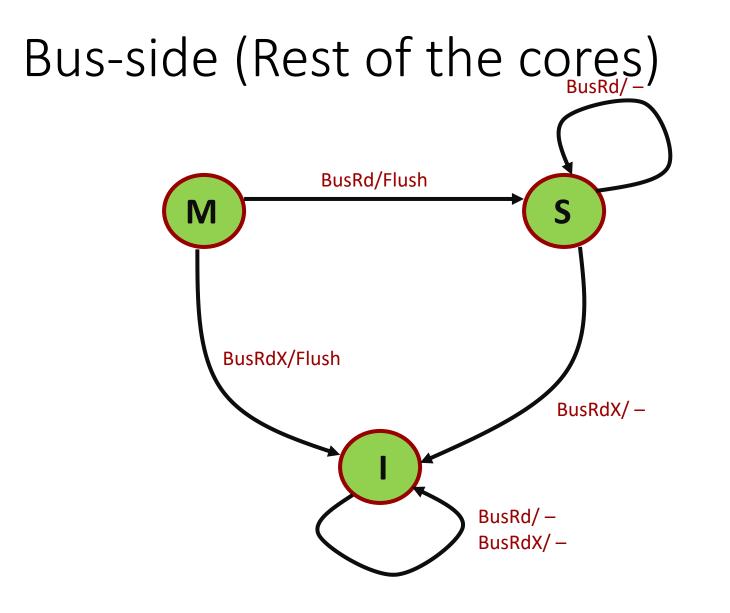

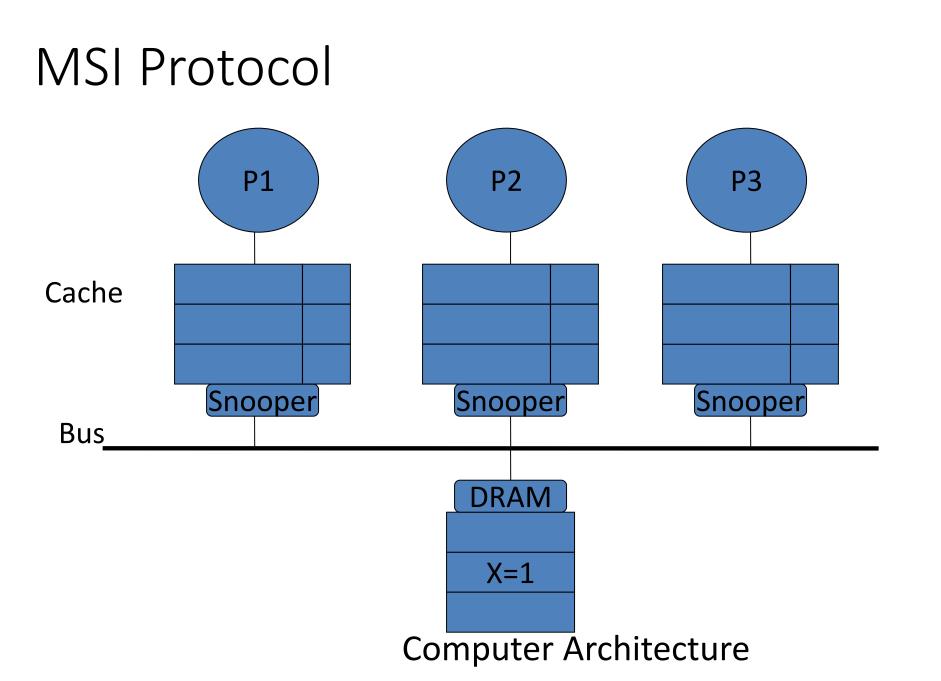

# A Simple MSI protocol

- Extend single valid bit per line to three states:

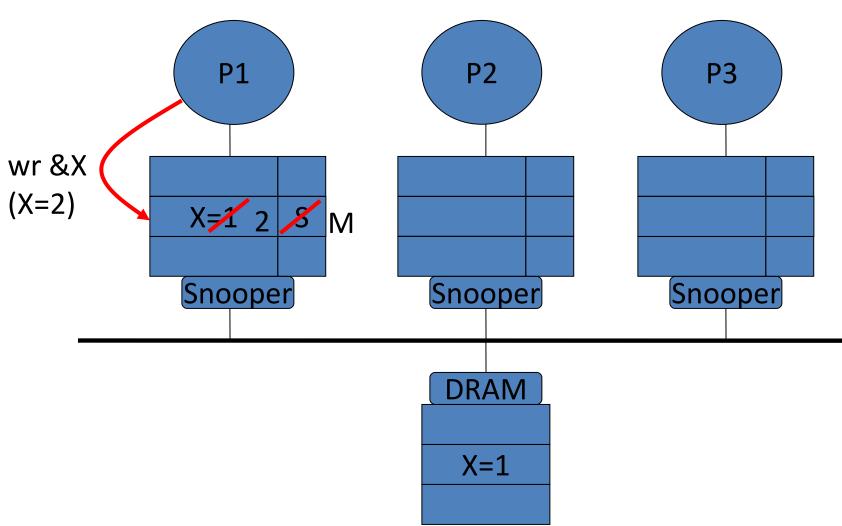

- □ **M**(odified): only one cache, memory not updated.

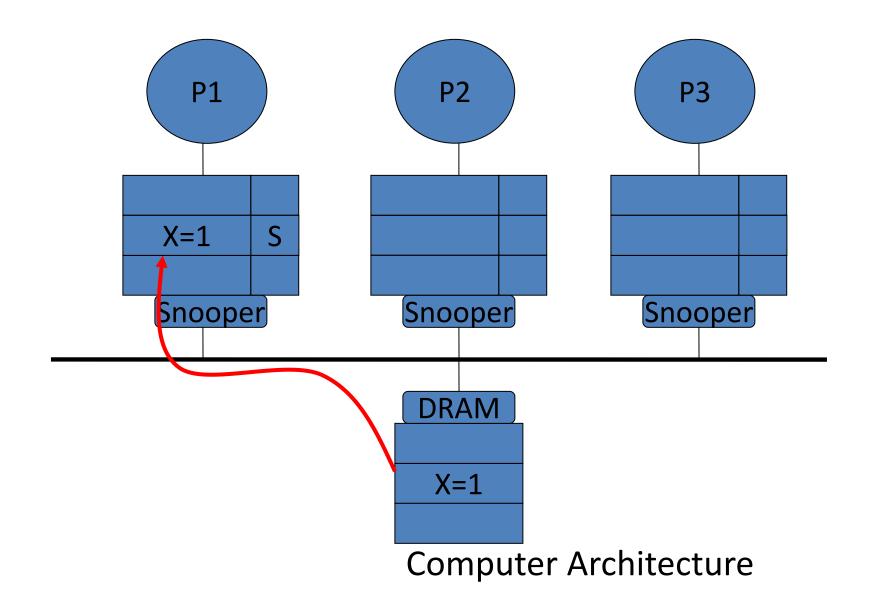

- S(hared): one or more caches, and memory copy is up-to-date

- □ I(nvalid): not present

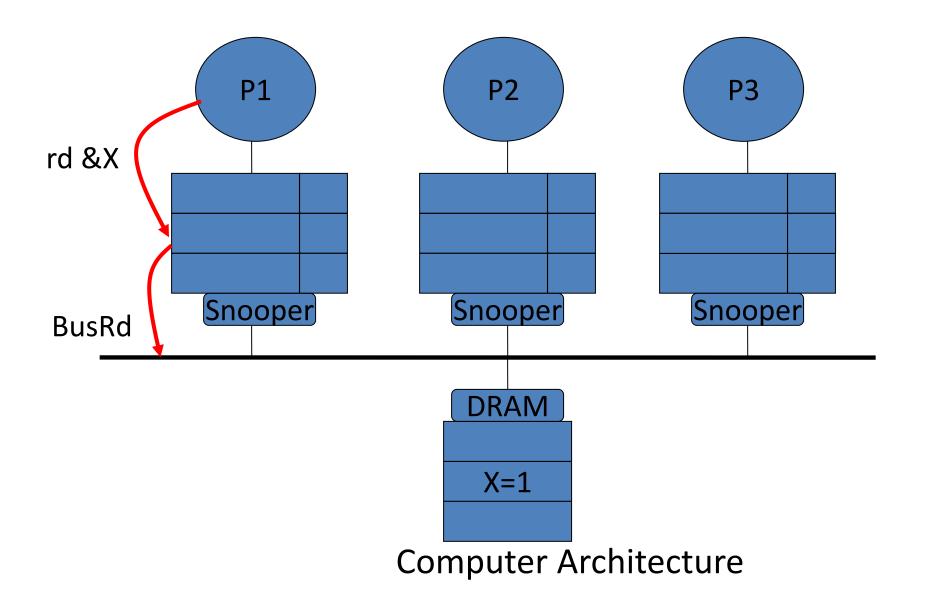

Read - *Read* request on bus, transitions to **S** Write - *ReadEx* request, transitions to **M** state

## State-transitions: Processor side (Master core)

# Summary: For your practice

| Proc<br>Action | State P1 | State P2 | State P3 | Bus<br>Action | Data<br>From |

|----------------|----------|----------|----------|---------------|--------------|

| R1             | -        | -        | -        | BusRd         | Mem          |

| W1             | -        | -        | -        | BusRdX        | Mem          |

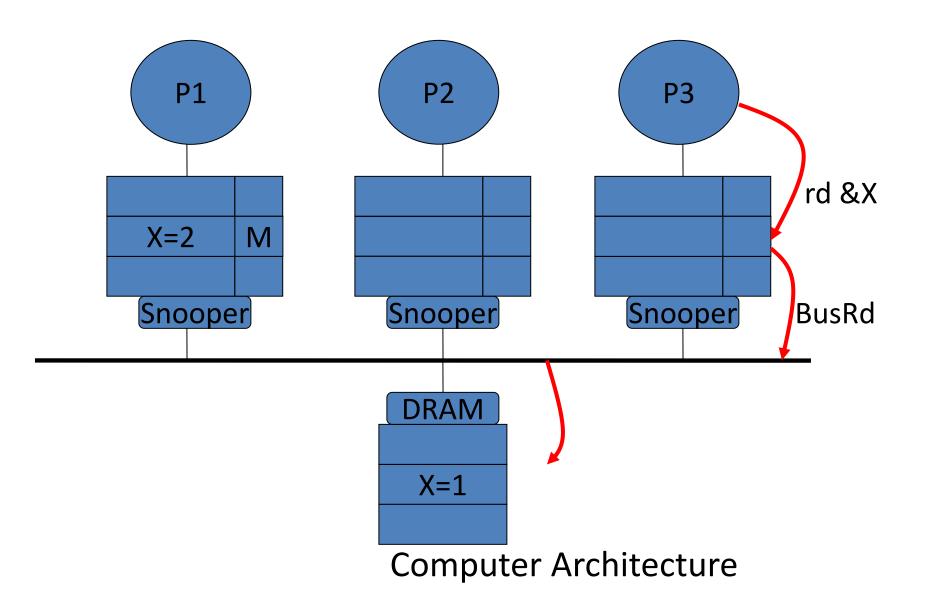

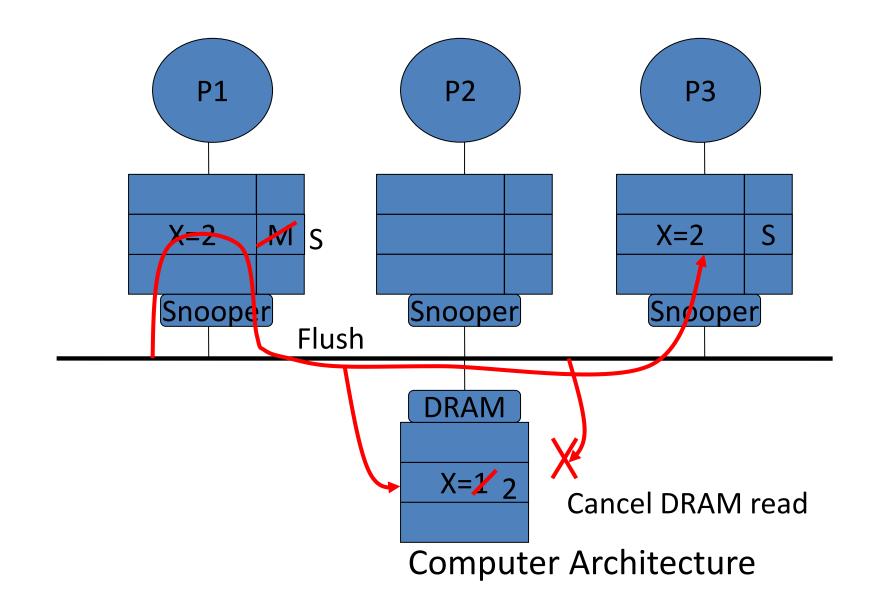

| R3             | -        | -        | -        | BusRd         | P1 cache     |

| W3             | -        | -        | -        | BusRdX        | Mem          |

| R1             | -        | -        | -        | BusRd         | P3 cache     |

| R3             | -        | -        | -        | -             | -            |

| R2             | -        | -        | -        | BusRd         | Mem          |

# Summary: For your practice

| Proc<br>Action | State P1 | State P2 | State P3 | Bus<br>Action | Data<br>From |

|----------------|----------|----------|----------|---------------|--------------|

| R1             | S        | -        | -        | BusRd         | Mem          |

| W1             | М        | -        | -        | BusRdX        | Mem          |

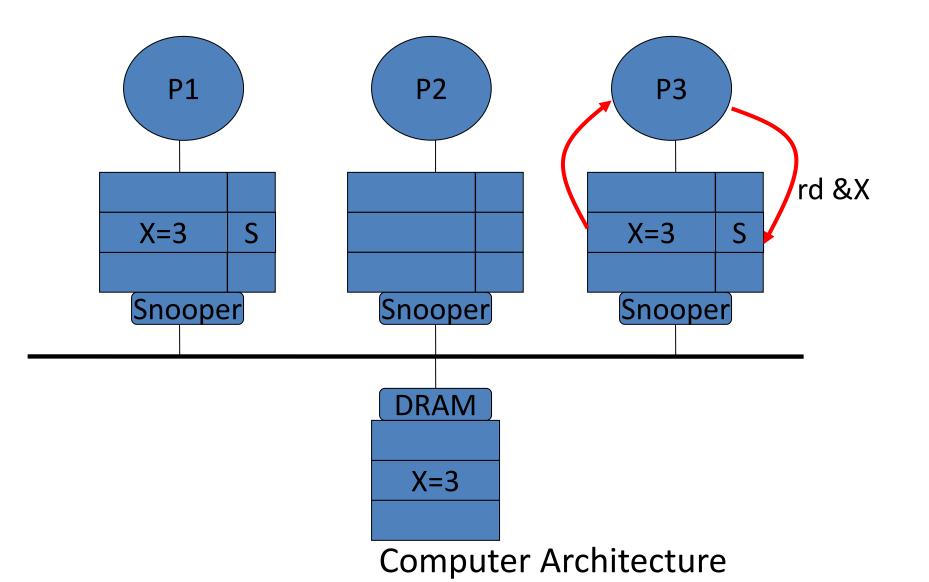

| R3             | S        | -        | S        | BusRd         | P1 cache     |

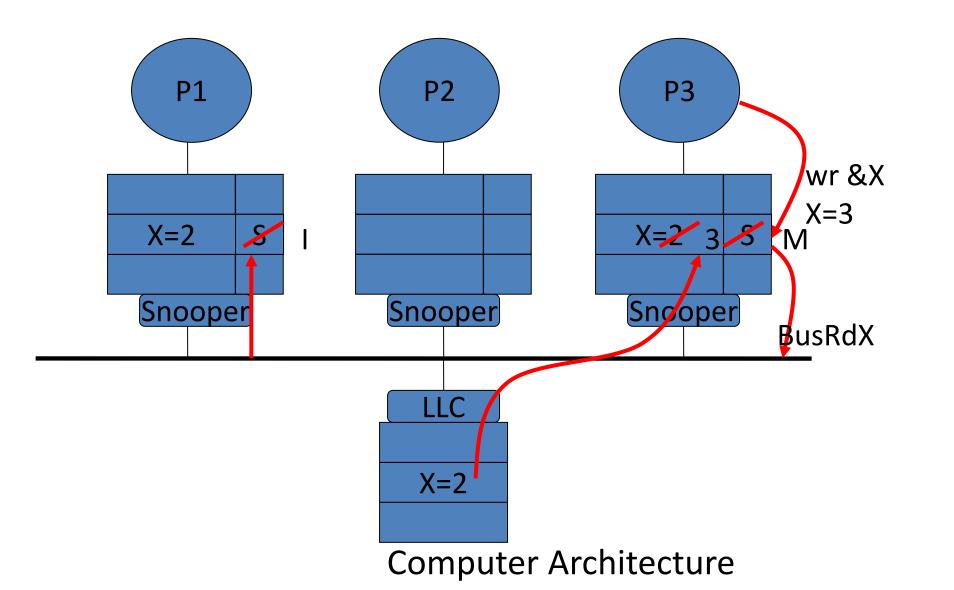

| W3             | I        | -        | М        | BusRdX        | Mem          |

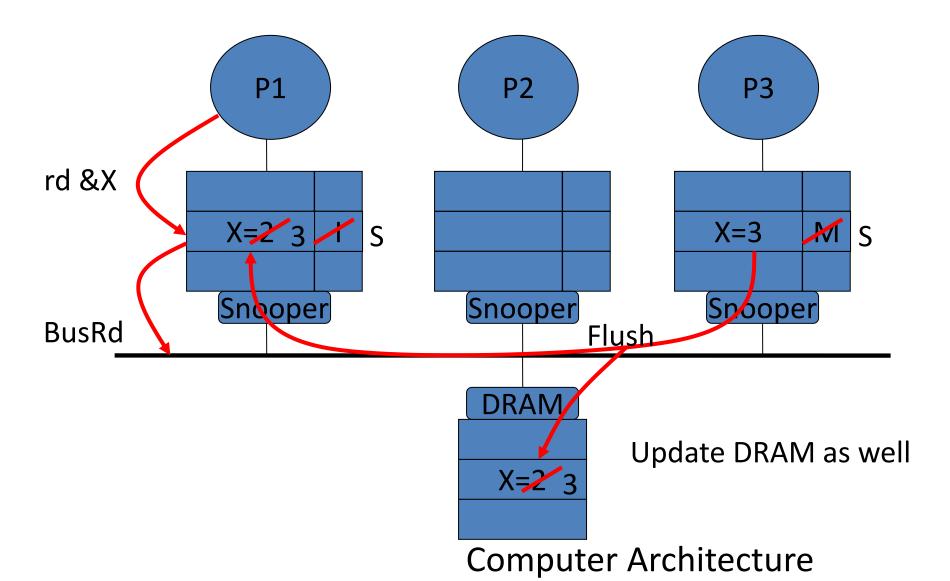

| R1             | S        | -        | S        | BusRd         | P3 cache     |

| R3             | S        | -        | S        | -             | -            |

| R2             | S        | S        | S        | BusRd         | Mem          |

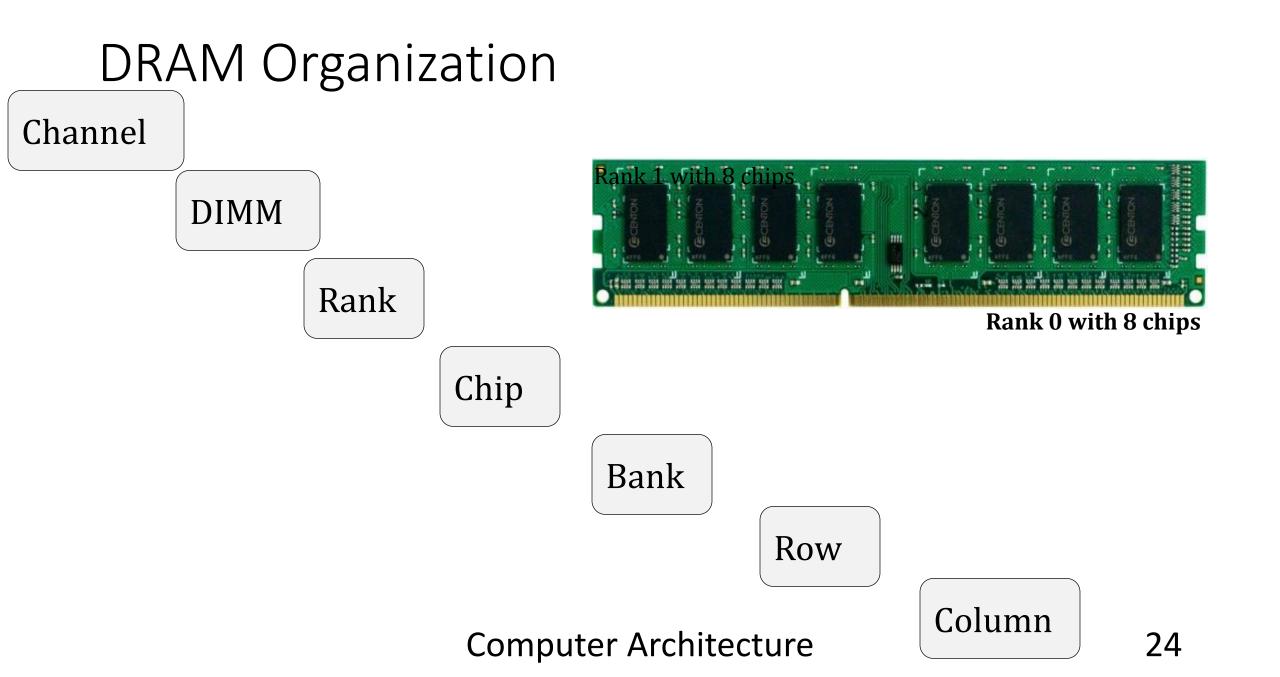

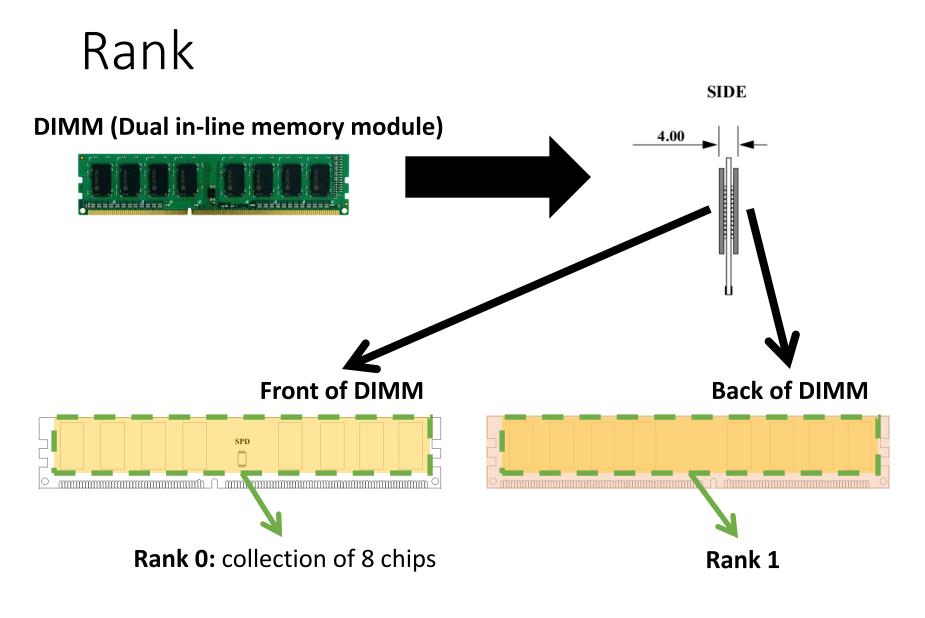

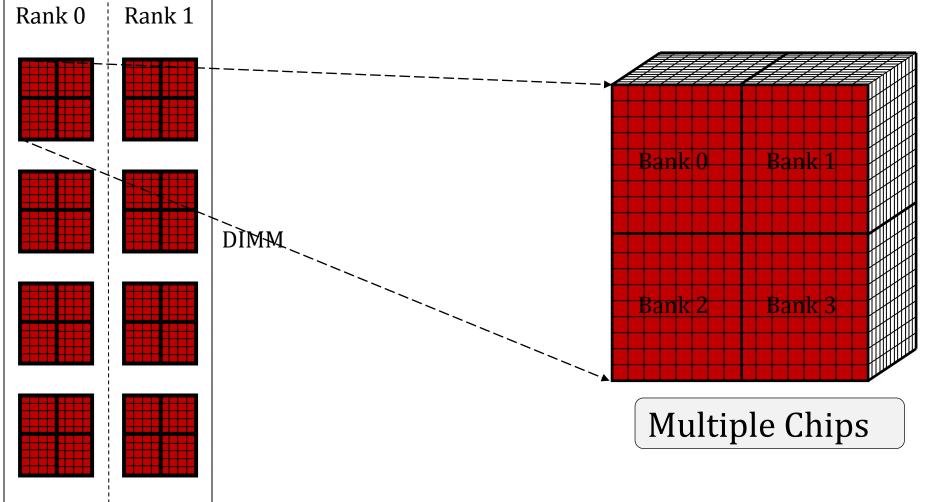

# Ranks, Banks, Rows, Columns

# ତୁମର ଦିନ ଶୁଭମୟ ହଉ