# CS230: Digital Logic Design and Computer Architecture

Lecture 9: Addressing Modes and ISA/Microarch.

https://www.cse.iitb.ac.in/~biswa/courses/CS230/main.html

#### Phones on Silence

If you are busy,

Then you may not consider making others busy ③

# Recap

| Name | Format |    |    | Exan | Comments |   |    |                           |

|------|--------|----|----|------|----------|---|----|---------------------------|

| add  | R      | 0  | 18 | 19   | 17       | 0 | 32 | add \$s1,\$s2,\$s3        |

| sub  | R      | 0  | 18 | 19   | 17       | 0 | 34 | <b>sub</b> \$s1,\$s2,\$s3 |

| addi | I      | 8  | 18 | 17   | 100      |   |    | <b>addi</b> \$s1,\$s2,100 |

| lw   | I      | 35 | 18 | 17   | 100      |   |    | lw \$s1,100(\$s2)         |

| SW   | I      | 43 | 18 | 17   | 100      |   | I  | <b>sw</b> \$s1,100(\$s2)  |

S1, s2, and s3 are R17, R18, and R19, respectively.

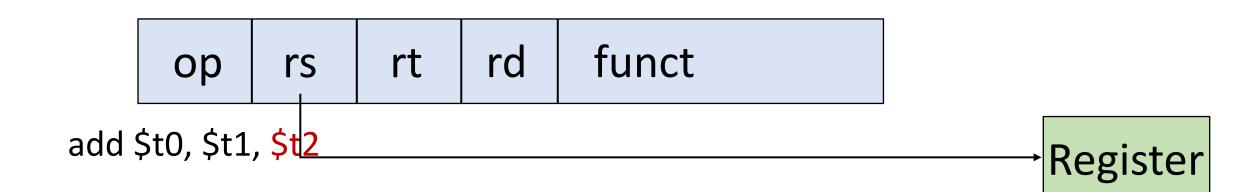

For lw/sw, the address of interest is address stored in s2 + 100

# Addressing Modes

# (How and where to find the data)

170

130

120

MON

Sal

Thu Fri

Immediate

|  | ор | rs | rt | Immediate |

|--|----|----|----|-----------|

|--|----|----|----|-----------|

addi \$t0, \$t1, 5

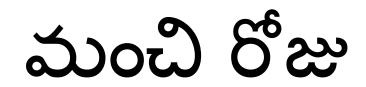

Register

Base (Arrays, structures, pointers)

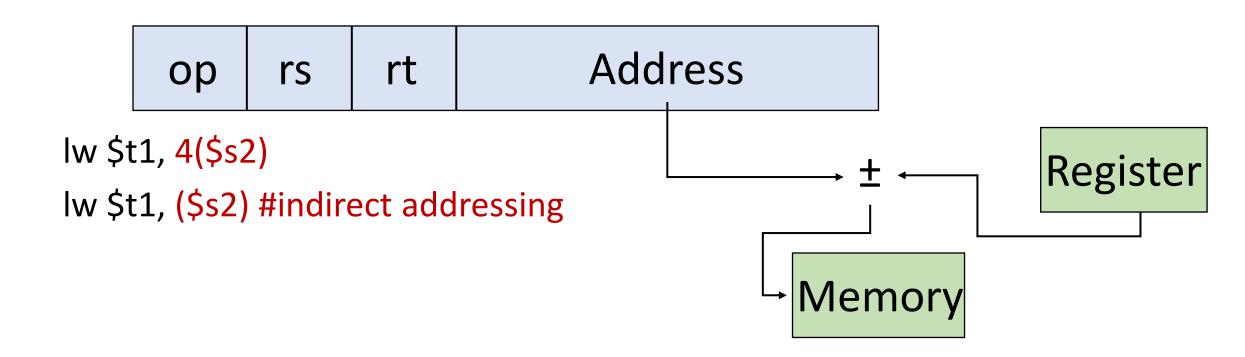

PC-relative (e.g., conditional branches, need an offset)

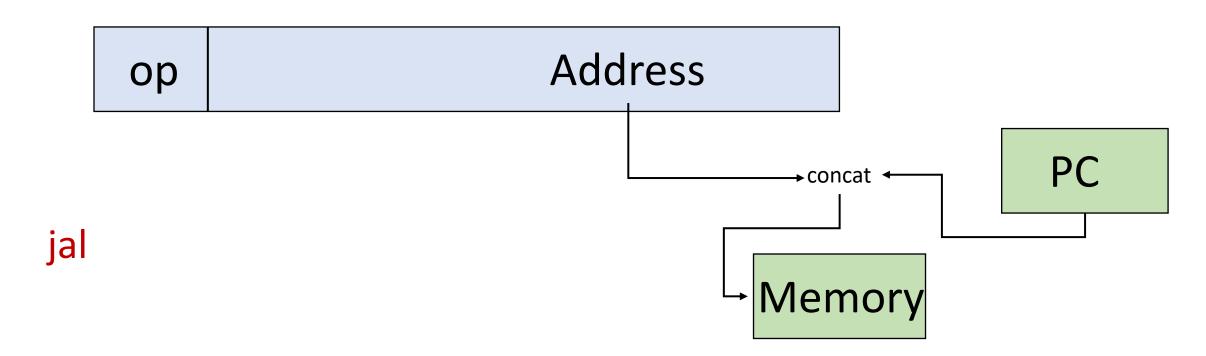

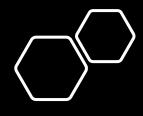

Pseudodirect

### Example

10

## Revisiting ISA and Microarchitecture

#### Microarchitecture (Not exposed to us)

- Implementation of an ISA

- Programmer cannot see/access it

ISA:

add instruction

Microarch:

Implementation of an adder (ripple carry)

#### ISA: What does it provide? Opcodes,

- Addressing Modes,

- Instruction Types and Formats,

- Registers

- Access control: user/OS

- Address space,

- Addressability,

- Alignment

#### ISA: What does it provide?

- Instructions:

- Opcodes,

- Addressing Modes,

- Instruction Types and Formats,

- Registers

- Access control: user/OS

Memory: Address space,

Addressability,

Alignment

# ISA must satisfy the needs of the software: - assembler, compiler, OS,

Microarchitecture

#### Rest of C230 after ISA ③

# Caches Memory Controllers Branch Predictors, Prefetchers, ...

#### Microarchitecture

Processor is in state S

Processor moves to state SS

Computer Architecture

Instruction

#### State

The information held in the processor at the end of an instruction to provide the processing context for the next instruction.

#### Computer Architecture

#### ISA + Microarchitecture

#### Based on lectures so far

#registers

#cycles to access a register

#Width of the register (32/64 bit)

#Instruction that uses register to access memory

#cycles to access memory

#### Based on lectures so far

#registers: ISA

#cycles to access a register: Microarch.

#Width of the register (32/64 bit) : ISA

#Instruction that uses register to access memory: ISA

#cycles to access memory: Microarch.

x86: It has 128/256-bit registers and one-bit too 😳

#### Where to place it?

- Closer to high-level language → Small semantic gap, complex instructions

(CISC kinda? e.g. quicksort an instruction <sup>(C)</sup>)

- Closer to hardware? → Large semantic gap, simple instructions (RISC kinda?)

- Remember: Compiler+ISA defines app's instruction count

#### And then the Debate of RISC vs CISC

RISC: Reduced Instruction Set of Computers Very few simple instructions Example: MIPS

CISC: Complex Instruction Set of Computers Lots of complicated instructions Example: x86 kind of ⓒ [x86 is CISC with RISC mysteries]

#### Mystery

INTEL *CONVERTS* CISC ONES INTO RISC ONES, AND GENERATE MICROOPERATIONS. INTELLIGENT CISC-RISC DECODER

CONSUMES AROUND 2% OF THE CHIP AREA. GOOD OR BAD? How Easy?

A billion-dollar idea 😳

- i) requires changes to microarchitecture.

- ii) requires changes to ISA.

- iii) both (i) and (ii)

Think about the trade-offs <sup>(C)</sup> Does it affect the system stack?

# The Other ISAs

#### World of ISAs

x86: Intel, AMD: Laptops, Desktops, Servers ARM: Arm, Qualcomm, Apple, Samsung: Mobiles E.

btw ARM: Advanced RISC Machines 🙂

RISC-V: Open-source ISA, what does it mean?

#### RISC-V, opensource

#### What is the license model?

The RISC-V ISA is free and open with a permissive license for use by anyone in all types of implementations. Designers are free to develop proprietary or open source implementations for commercial or other exploitations as they see fit. RISC-V International encourages all implementations that are compliant to the specifications.

Note that the use of the RISC-V trademark requires a license which is granted to members of RISC-V International for use with compliant implementations. The RISC-V specification is based around a structure which allows flexibility with modular extensions and additional custom instructions/extensions. If an implementation was based on the RISC-V specification but includes modifications beyond this framework, then it cannot be referenced as RISC-V.

#### Does that mean free for industry to use and play with, but then we pay if we produce a product using this ISA?

The RISC-V ISA is free for product use too. Those who want to use the RISC-V logo should join RISC-V International (see question No. 1).

If our company builds a RISC-V implementation, is it required to release its source code for the RISC-V core?

No, the source code can be completely closed.

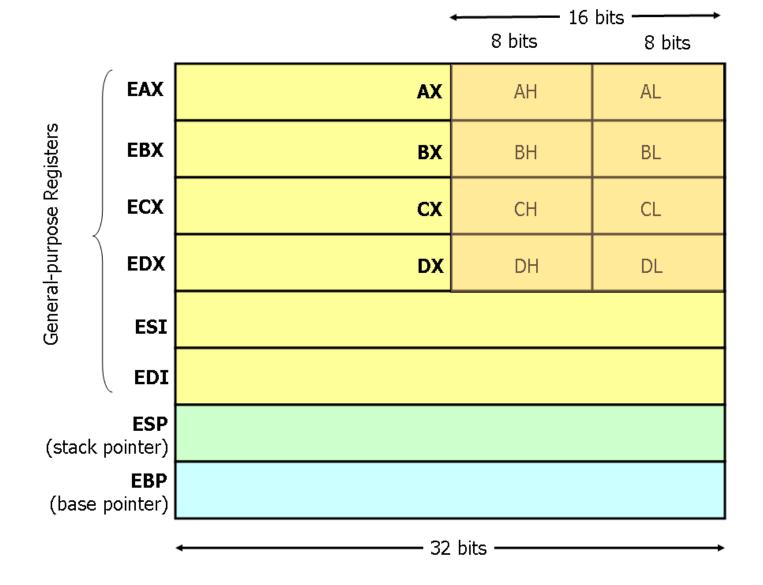

# x86 Registers: 80386 For 64-bits, rax, rbx

#### Subtle Differences

x86 arithmetic/logic instructions: one operand should act as both source and destination

add \$s0, \$s1 // Add \$s0 and \$s1 and put it in \$s0 🙂

One of the operands can be in memory:

wow (programmer) or oh no (instruction size ☺) !!

add \$s0, Mem[\$s1] ☺

No more fixed-length instructions <sup>(2)</sup> can be 4/8/X bytes

Why?

#### Fixed Width or Variable Width

Variable: No fixed size6 bytes for add, 2 bytes for loadSmaller code footprint (compact)

Fixed:

4 bytes for all, Larger code footprint, simple decoding

#### Fallacies

CISC instructions provide higher performance

Assembly language codes provide higher performance

Q3

Q3

1-00

1,000

### Coffee Credits

Dhananjay: +1 Yashwant: +2