# CS305: Computer Architecture Single Cycle CPU cont.

https://www.cse.iitb.ac.in/~biswa/courses/CS305/main.html

https://www.cse.iitb.ac.in/~biswa/

# Control Signals So far

Read

address

Instruction s [31-0]

Instruction

memory

- MemRead

- MemWrite

- RegWrite

- MemtoReg

- RegDst

- ALUop, ALUSrc

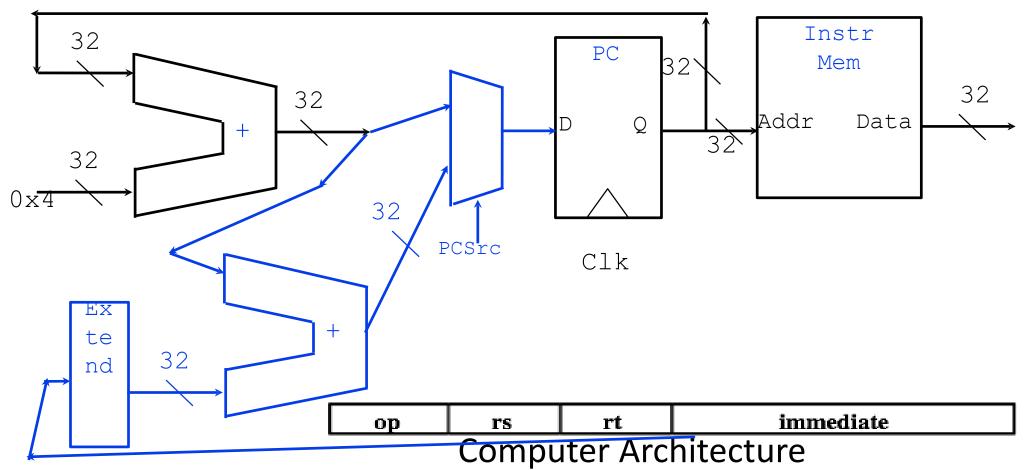

- PCSrc (we have not discussed about the branch)

**Computer Architecture**

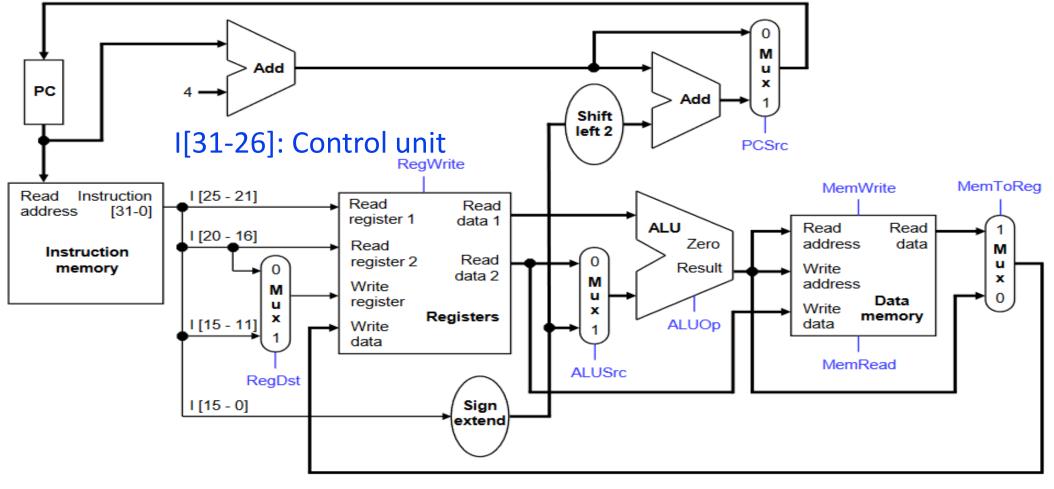

I [31 - 26]

I [5 - 0]

Zero

RegDst

RegWrite

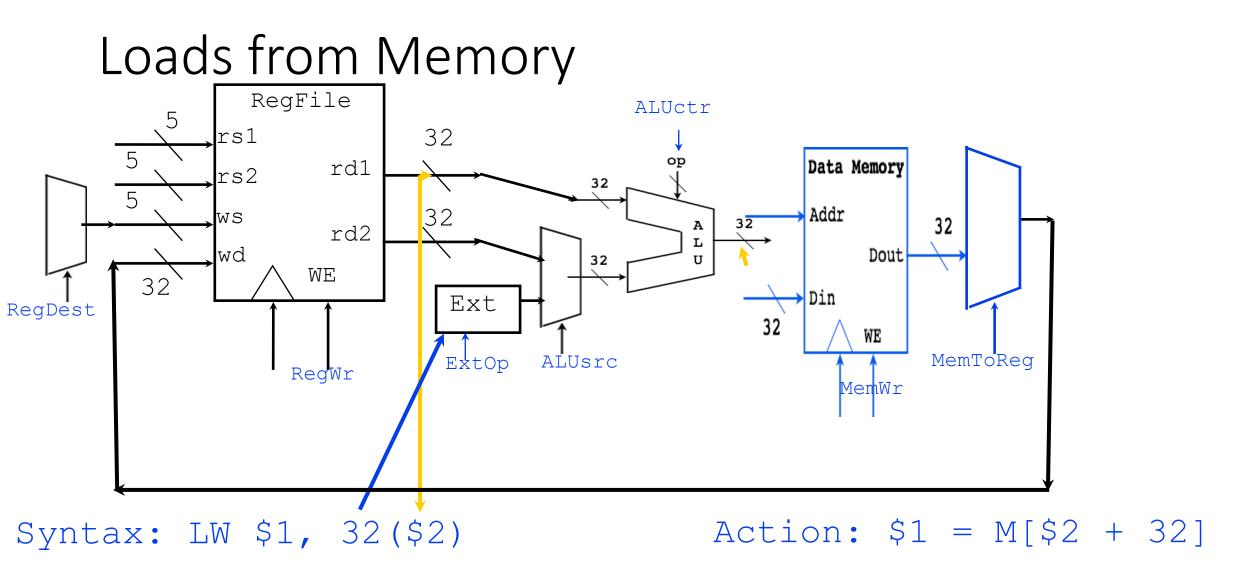

ALUSrc

ALUOp

Control

MemWrite

MemRead

MemToReg

4

PCSrc

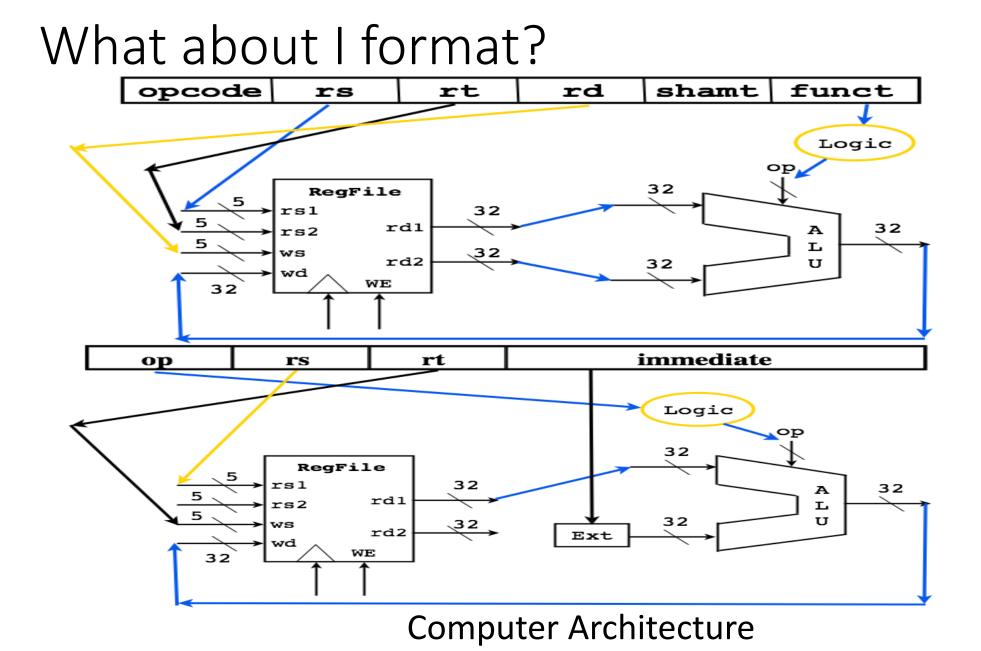

#### Branch Instructions Syntax: BEQ \$1, \$2, 12 Action: If (\$1 != \$2), PC = PC + 4 Action: If (\$1 == \$2), PC = PC + 4 + 48

#### In detail

- MemRead: Read from memory when assert

- MemWrite: Write into the memory when assert

- RegWrite: Reg. on Write register updated with the input, on assert

- MemtoReg: On assert, memory to register, on deassert, ALU to register

- RegDst: On assert, use rd field, on deassert use rt field

- ALUSrc: On assert, lower 16 bits of an inst., on deassert from the second register

- PCSrc: On assert, branch target, deassert, PC+4

### Control Signal Table

| Operation | RegDst | RegWrite | ALUSrc | ALUOp | MemWrite | MemRead | MemToReg |

|-----------|--------|----------|--------|-------|----------|---------|----------|

| add       | 1      | 1        | 0      | 010   | 0        | 0       | 0        |

| sub       | 1      | 1        | 0      | 110   | 0        | 0       | 0        |

| and       | 1      | 1        | 0      | 000   | 0        | 0       | 0        |

| or        | 1      | 1        | 0      | 001   | 0        | 0       | 0        |

| slt       | 1      | 1        | 0      | 111   | 0        | 0       | 0        |

| lw        | 0      | 1        | 1      | 010   | 0        | 1       | 1        |

| SW        | X      | 0        | 1      | 010   | 1        | 0       | Х        |

| beq       | X      | 0        | 0      | 110   | 0        | 0       | Х        |

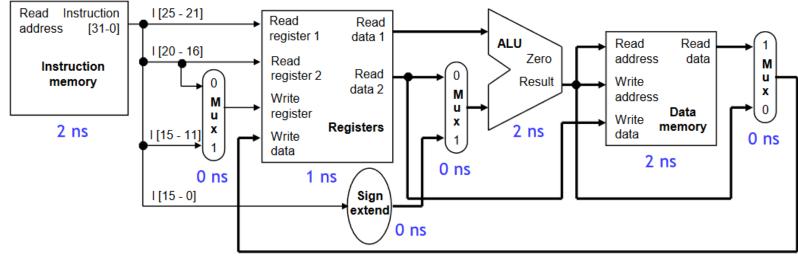

### The Complete Picture

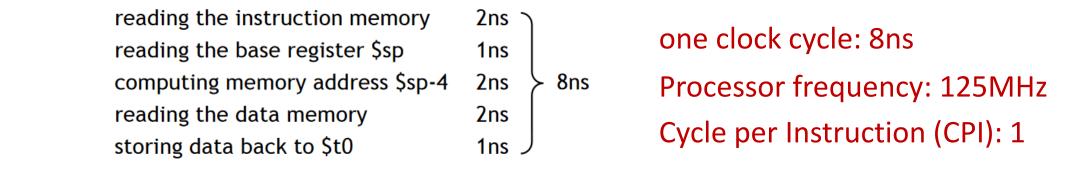

# Why not single cycle?

• The longest possible datapath is the clock cycle time.

What does it mean?

## Why not single cycle?

For example, lw \$t0, -4(\$sp) needs 8ns, assuming the delays shown here.

An add instruction: no need of 8ns

### Dhonnobad