# CS305: Computer Architecture Delayed Branch and Branch Delay Slots https://www.cse.iitb.ac.in/~biswa/courses/CS305/main.html

https://www.cse.iitb.ac.in/~biswa/

# What else can be done? Compiler?

Delayed branch: Define branch to take place AFTER a following instruction(used to be in early RISC processors)

branch instruction sequential successor<sub>1</sub> sequential successor<sub>2</sub>

> .....Branch delay of length *n* sequential successor<sub>n</sub> branch target if taken Computer Architecture

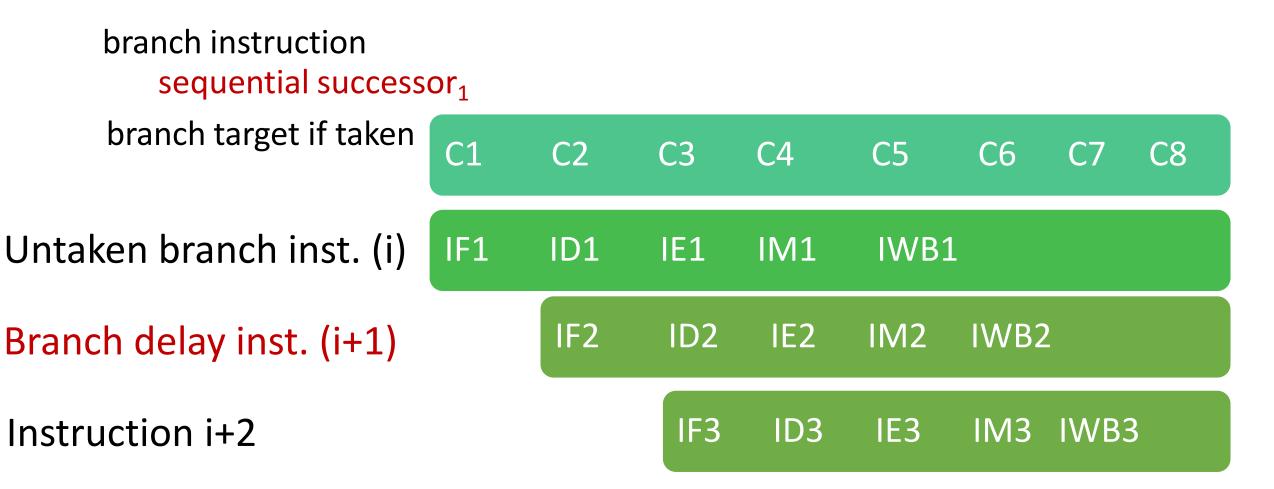

## One slot: Not Taken (untaken) branch

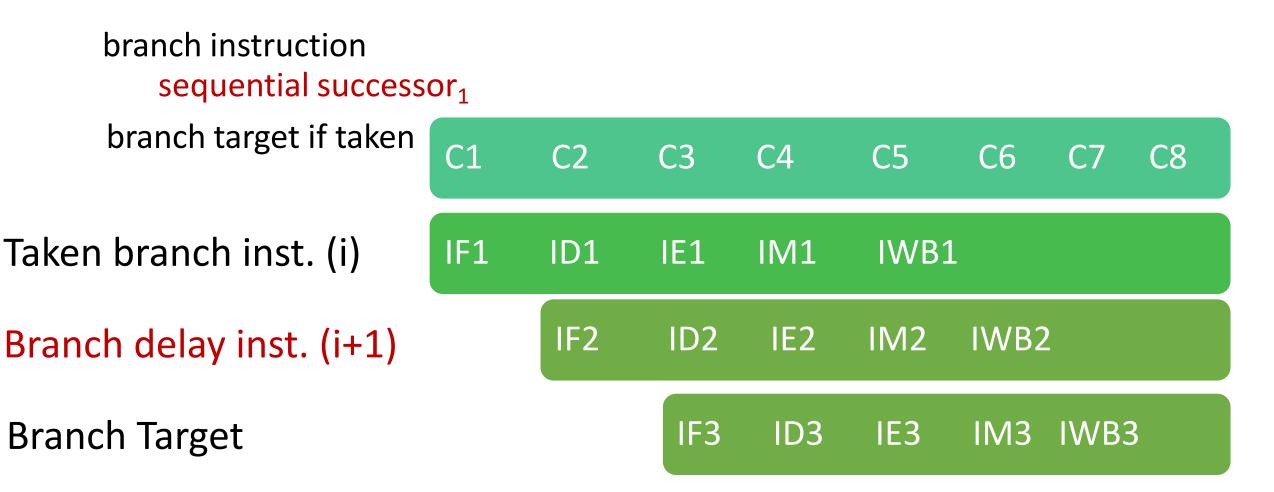

## One slot: Taken branch

## Word of Caution!

Do not put a branch in the branch delay slot 🛞

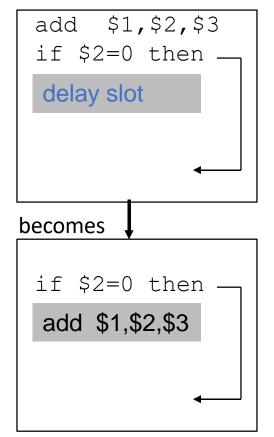

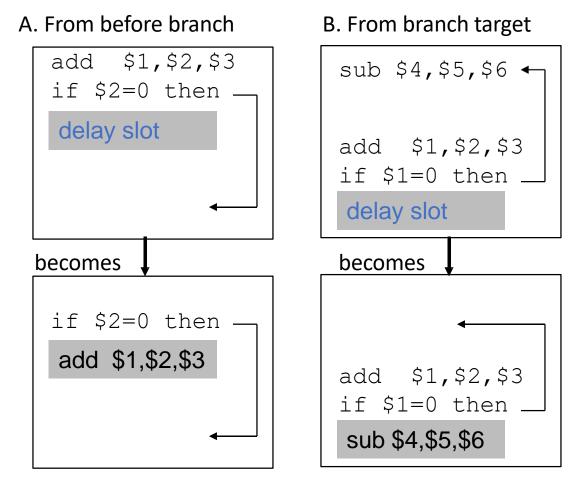

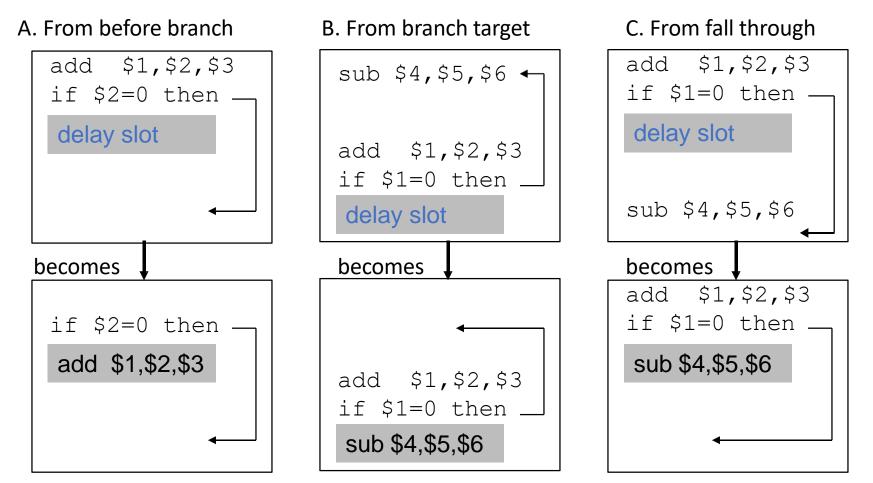

# Scheduling Branch Delay Slots

#### A. From before branch

A is the best choice, fills delay slot & reduces instruction count (IC) Computer Architecture

# Scheduling Branch Delay Slots

A is the best choice, fills delay slot & reduces instruction count (IC) Computer Architecture

7

# Scheduling Branch Delay Slots

#### A is the best choice

## Stalls and Performance

Ν

### For a program with N instructions and S stall cycles,

Average CPI = N

## Stalls and Performance

Ν

### For a program with N instructions and S stall cycles,

Average CPI = N+S

## New Pipeline Speedup

### Pipeline Speedup = Pipeline Depth

### 1+pipeline stalls because of branches

### Pipeline stalls (branches) = Branch frequency X penalty

### Summary

#### Data Hazards

Bypassing/forwarding

Stalls (NOPs) – if no scope for bypassing

#### **Control** hazards

Speculate, PC=PC+4, kill the wrong path

Delayed branch with the help of branch delay slots, new pipeline speedup