# CS305: Computer Architecture Caches-I

https://www.cse.iitb.ac.in/~biswa/courses/CS305/main.html

https://www.cse.iitb.ac.in/~biswa/

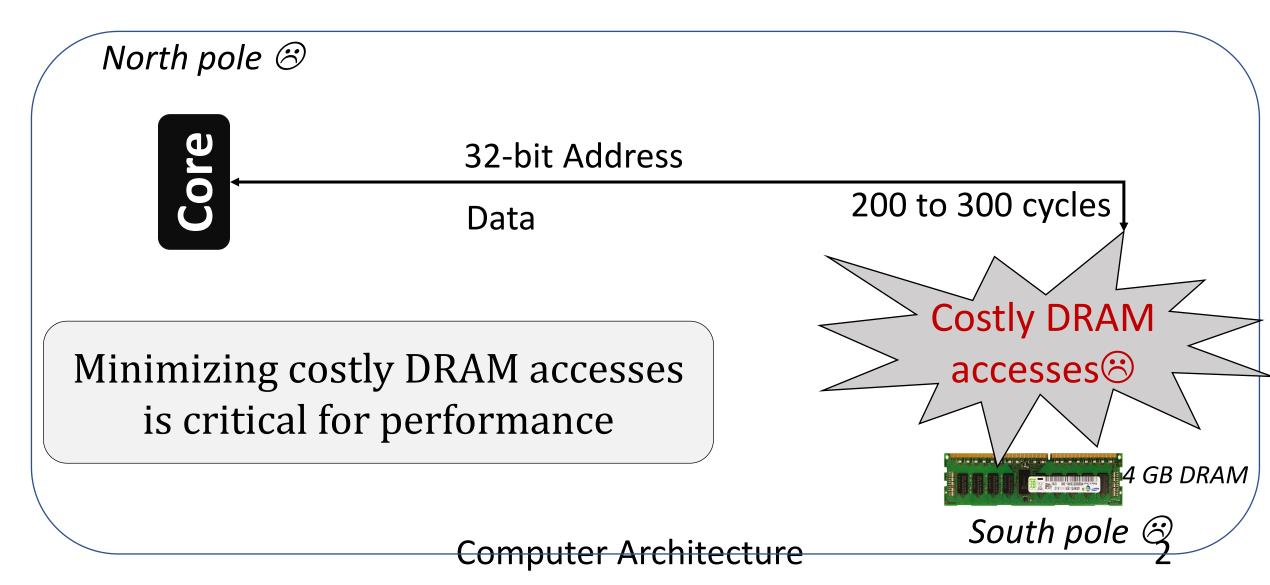

### World with no caches

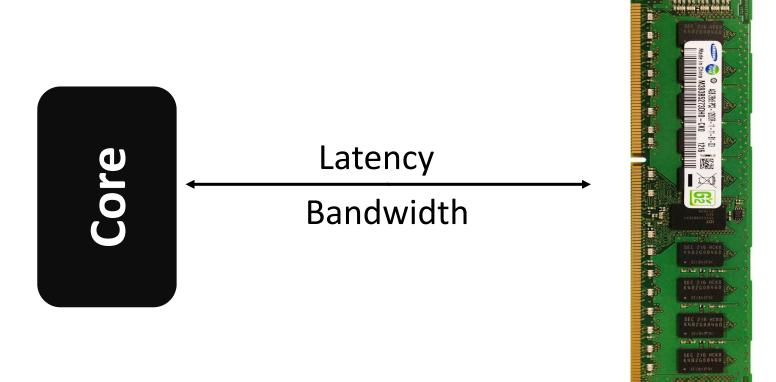

# Remember Latency and Bandwidth

Bandwidth problems can be cured with money. Latency problems are harder because the speed of light is fixed – you can't bribe God

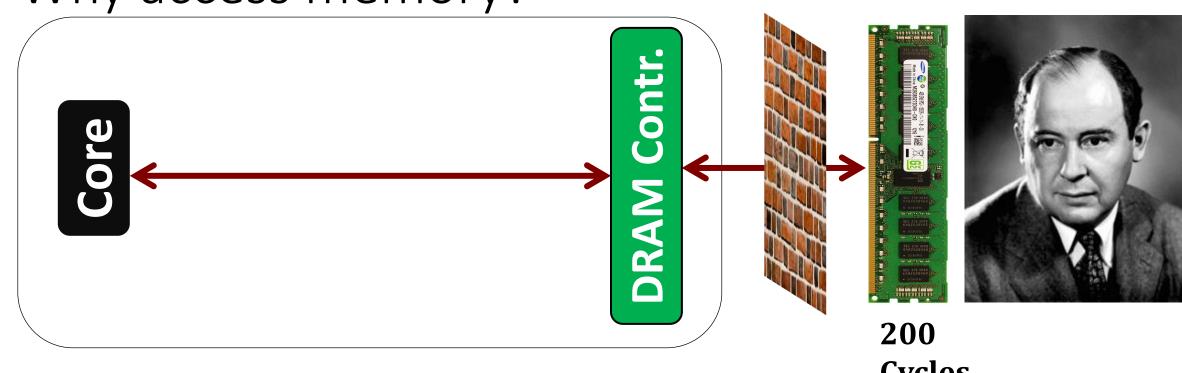

### Why access memory?

Cycles

Memory stores CODE and DATA Processor accesses for LOADs (reads) and STOREs(writes) Memory Wall: Grandmother of all the walls Computer Architecture

### Do not ignore the common case mantra

Reduction in DRAM accesses ~ Improvement in execution time

# WRONG!

First Law of Performance:

Make the common case fast

What if your program is not memory intensive

# Let's look at the Applications (benchmarks)

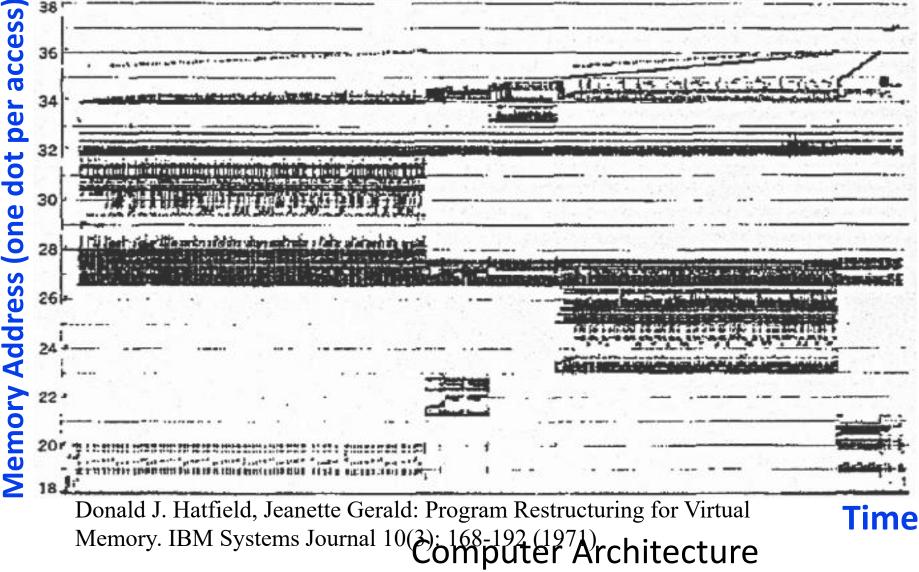

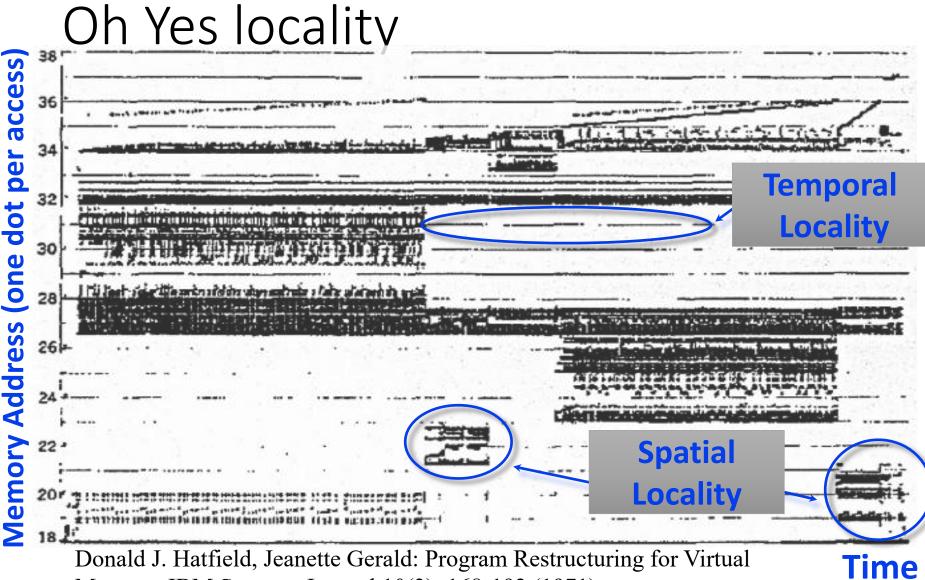

Donald J. Hatfield, Jeanette Gerald: Program Restructuring for Virtual Memory. IBM Systems Journal 10(3): 168-192 (1971) Computer Architecture

Few Examples

9

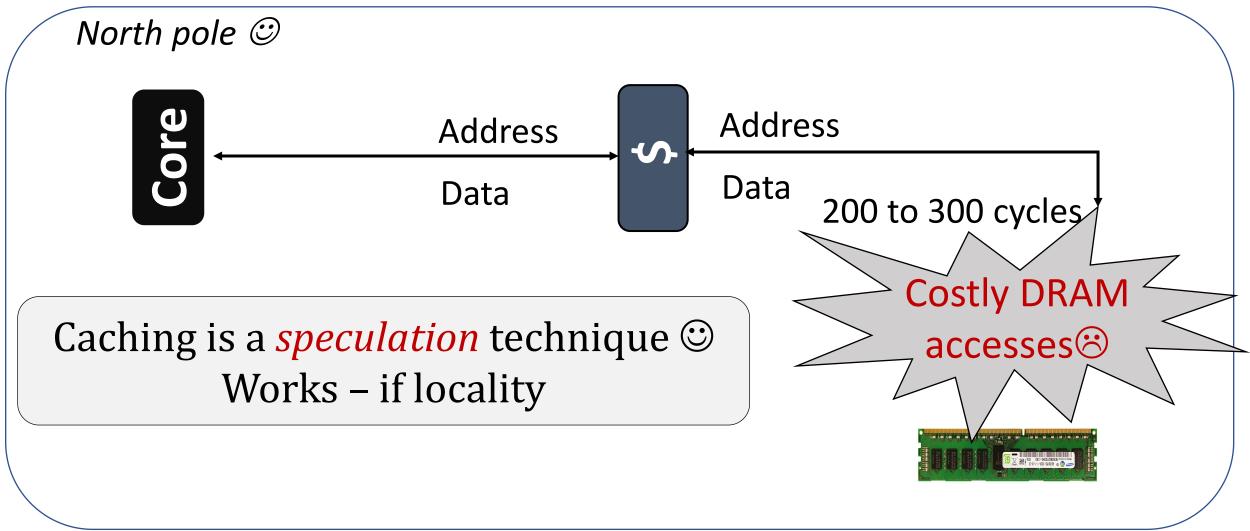

## Caching: 10K Feet View

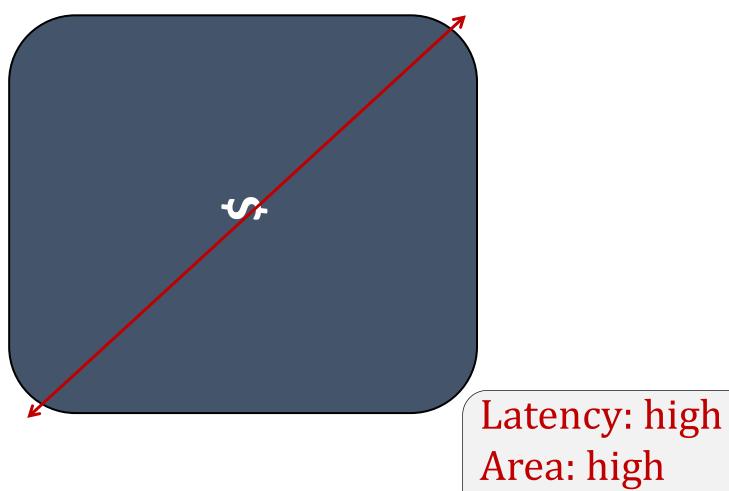

# How big/small?

Core

Latency: low Area: low **Capacity:** low

#### **Computer Architecture**

Capacity: high

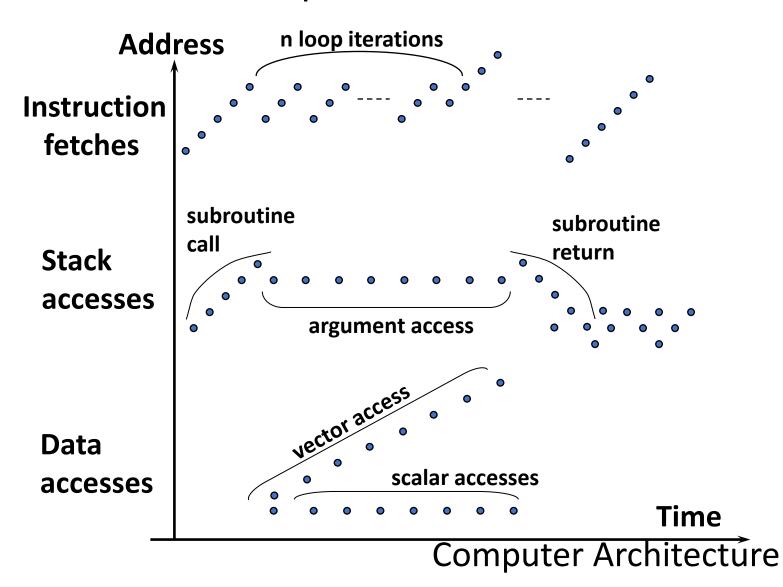

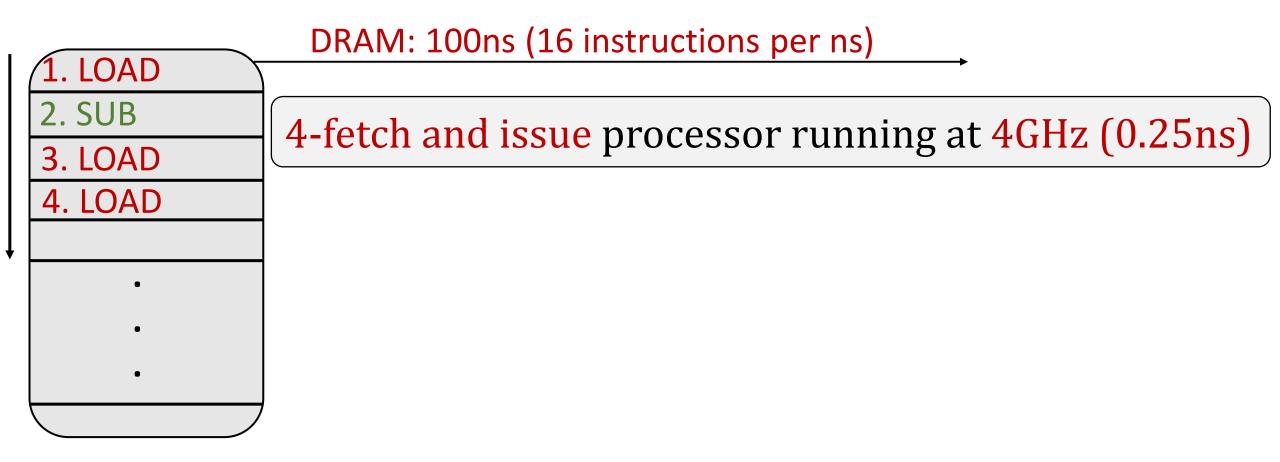

In-order Instruction Fetch (Multiple fetch in one cycle)

Processor core says all LOADs should take one cycle. Ehh!

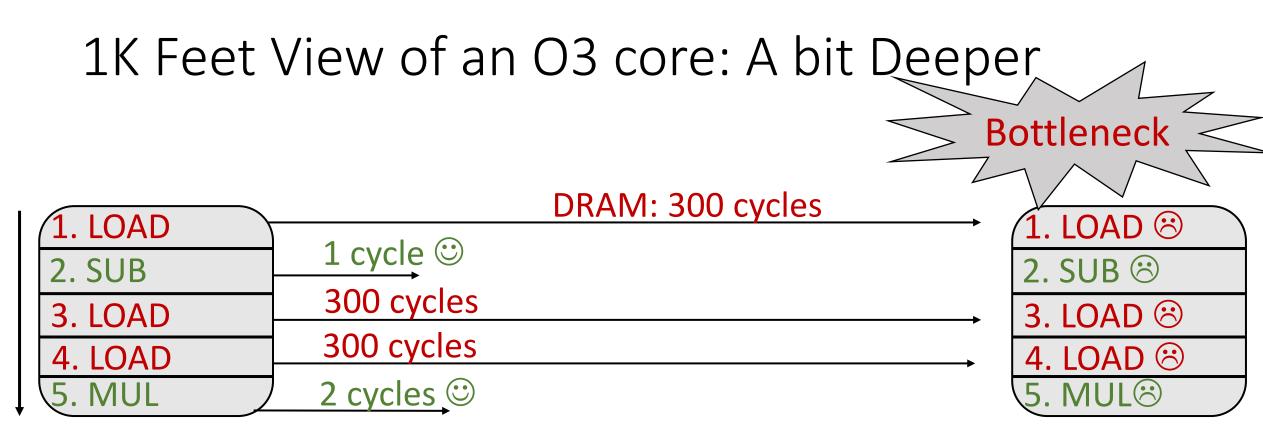

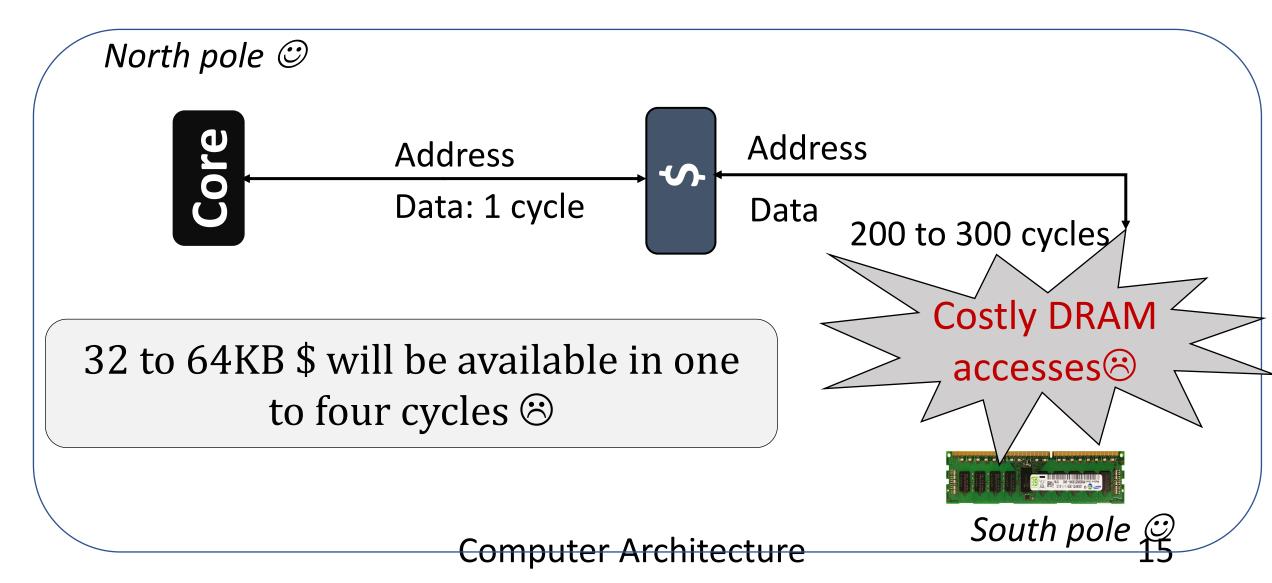

### Impact of one DRAM access

### Impact of one DRAM access

### Cache with latency

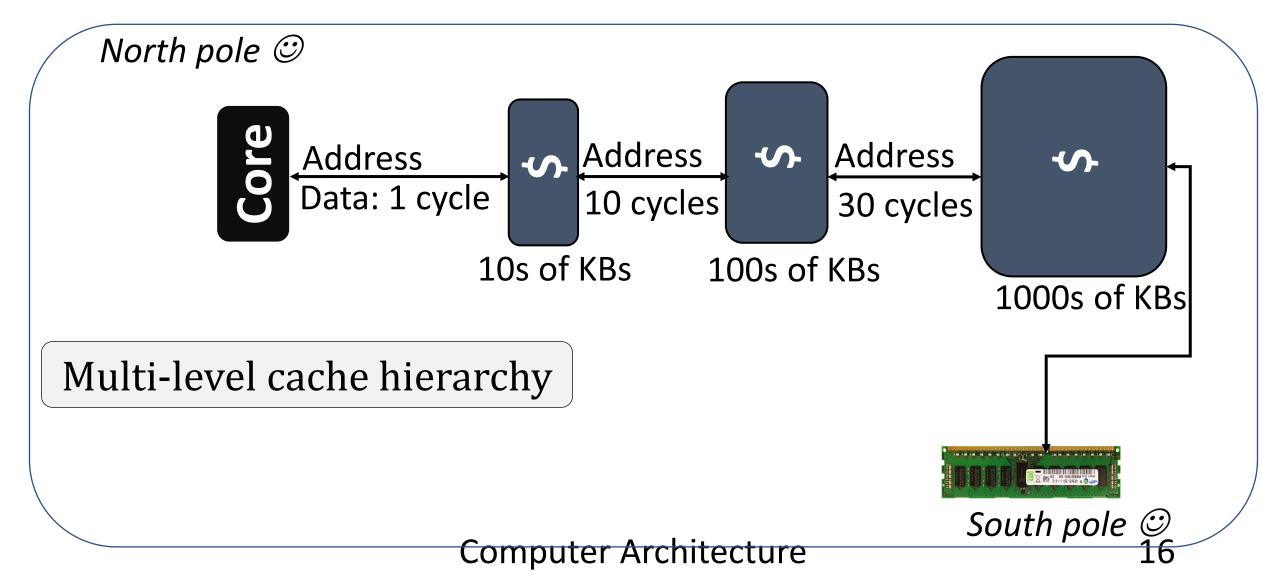

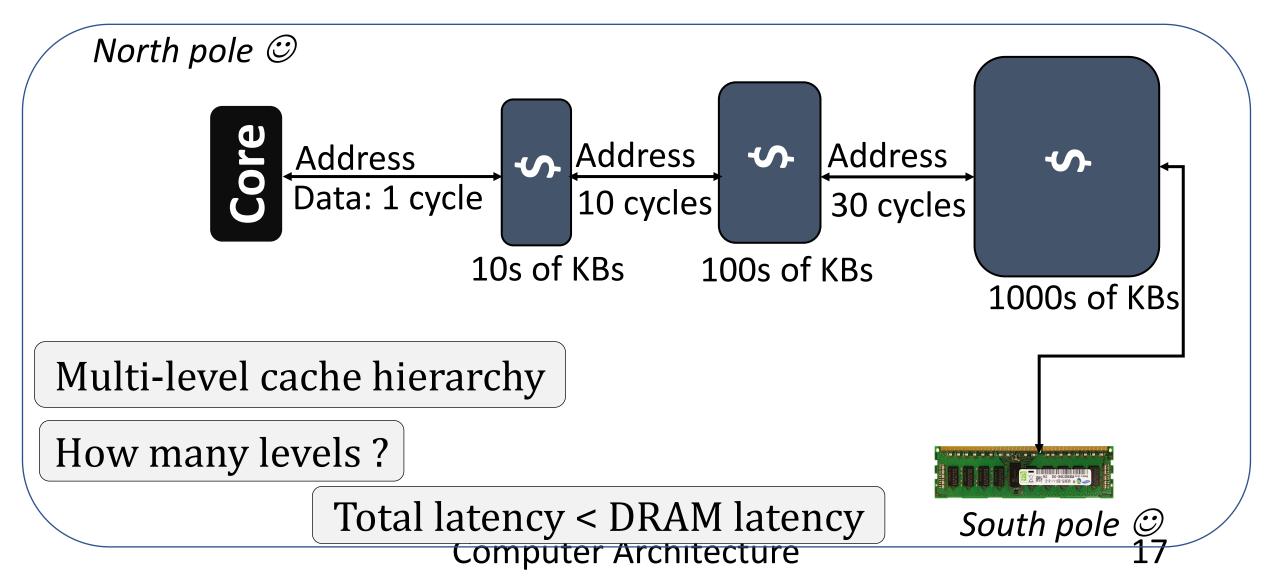

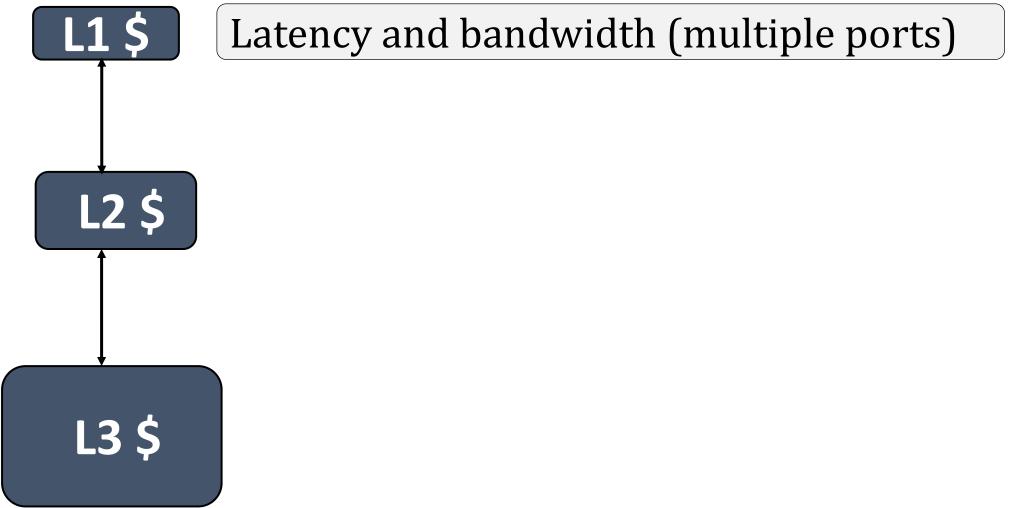

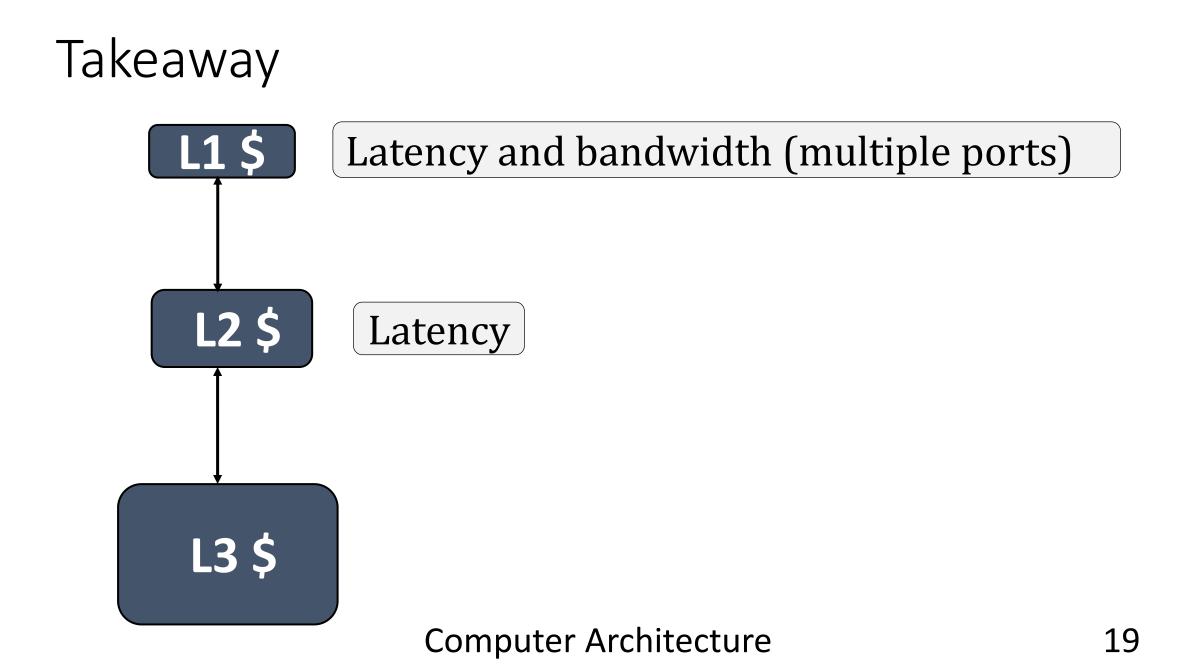

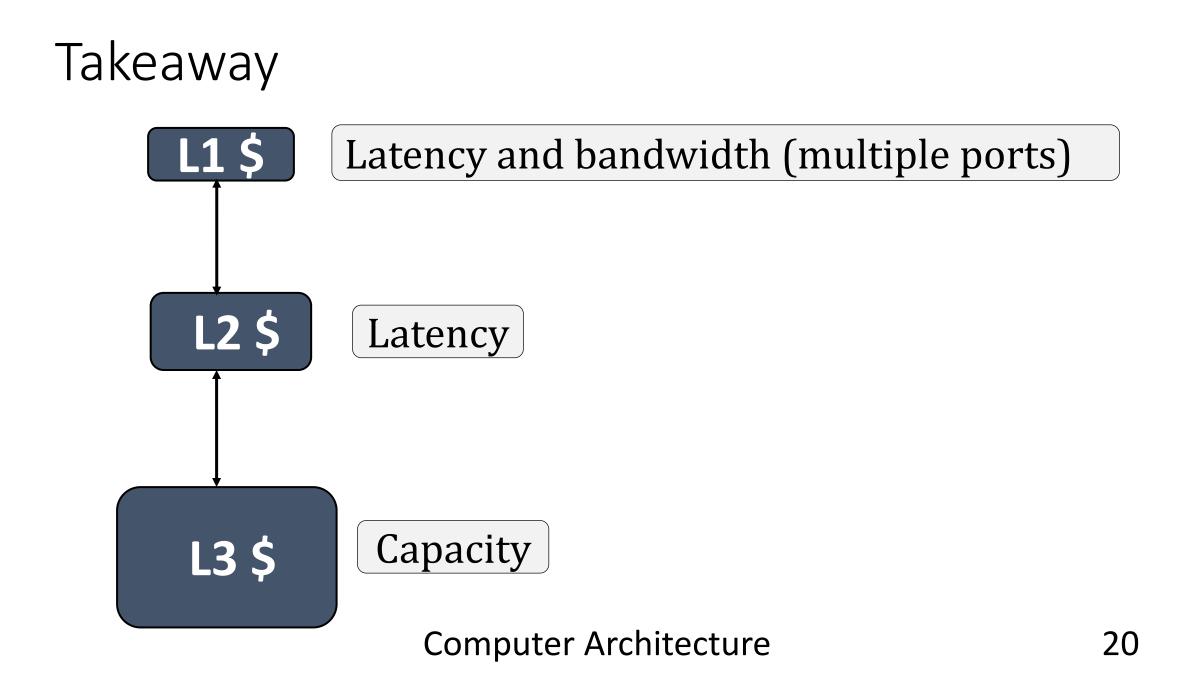

# Cache hierarchy with latency

# Cache hierarchy with latency

# Takeaway

# Ďakujem