# FRACTEL – Design, Implementation And Evaluation of a Multi-hop Wireless TDMA System

Nirav Uchat Faculty Mentors

Prof. Bhaskaran Raman and Prof. Kameswari Chebrolu

SYNERG MTP Defense Workshop June 24-25, 2009

Department of Computer Science and Engineering

IIT Bombay

### **Project Vision**

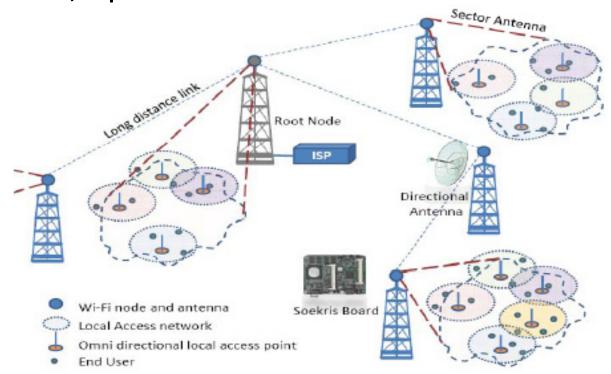

- Digital inclusion of remote villages

- Providing data, voice and video connectivity with QoS guarantees

- Cost effective solution by using off-the-shelf hardware, open source driver and license free band

## Challenges in Wireless

- Issues in using 802.11 Wi-Fi protocol

- Long distance carrier sensing

- Difficult to assure QoS guarantees

- Poor performance on long distance link

- How about using TDMA?

- Communication with precise slot boundaries; no CSMA

- Minimum collision due to synchronous operation

- Guaranteed fulfillment of QoS requirements due to centralized scheduling

- TDMA more suitable than CSMA for our requirements

### **Problem Statement**

To Design, Implementation and Evaluate Multi-hop WiFi-based TDMA System

- Using off-the-shelf hardware, open-source driver and unlicensed band

- Should support both best effort (HTTP, FTP) and real-time(voice, video) traffic

- Dynamically adapting the schedule in response to change in network load and topology

#### Related Work

- Existing protocols provide hooks into Madwifi drivers for

- stripping off CSMA mechanism (SoftMAC NOV, 2005)

- using different MAC protocols based on network conditions (MultiMAC - NOV, 2005)

- precise time synchronization (MadMAC SEP, 2006)

- control over radio configuration and time critical functions (FreeMAC - AUG, 2008)

- Different Approach

- Overlay MAC approach works above MAC layer (JUN, 2005)

- 2P Protocol on bipartite graph with marker packet HostAP driver on prism chipset – (AUG, 2005)

- SRAWAN IIT Kanpur (May, 2006)

- To our knowledge, there is no implementation of multi-hop TDMA system yet

### Our Approach

- Centralized TDMA scheduler

- Root node creates a global schedule and disseminates it across the network

- Adapting schedule based on bandwidth requests

- Multi-hop time synchronization and schedule dissemination mechanism

- Multi-hop packet routing

- Multi-hop TDMA implementation at MAC layer

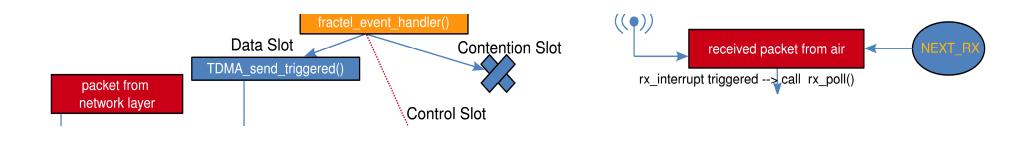

## Protocol Design 1 of 2

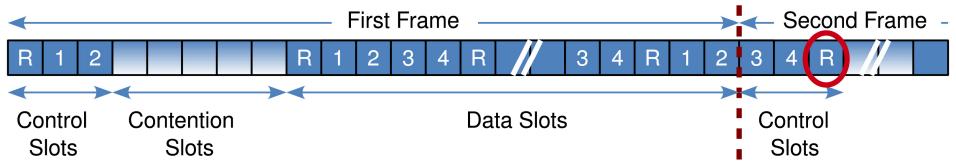

#### Slot types

- Control slot: Sending control information down the tree

- Contention slot: Sending information towards root node

- Data slot: Sending data across network

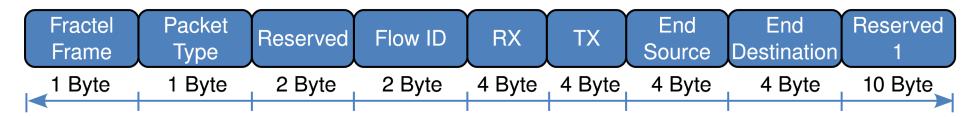

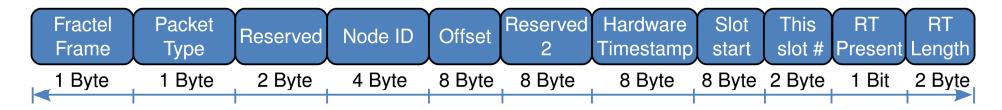

#### Packet Headers

- Schedule Header: Attached to every schedule packet

- Data Header: Attached to every data packet

#### Frame Structure

- Few control and contention slots and many more data slots

- Repeating pattern of these slots(but fixed for single frame)

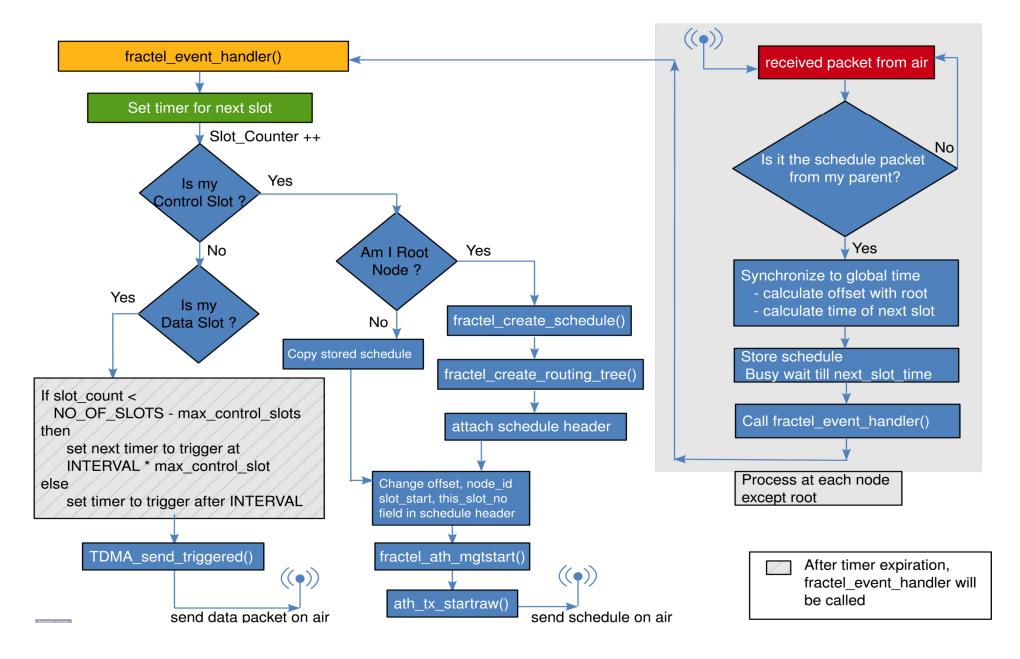

### Protocol Design 2 of 2

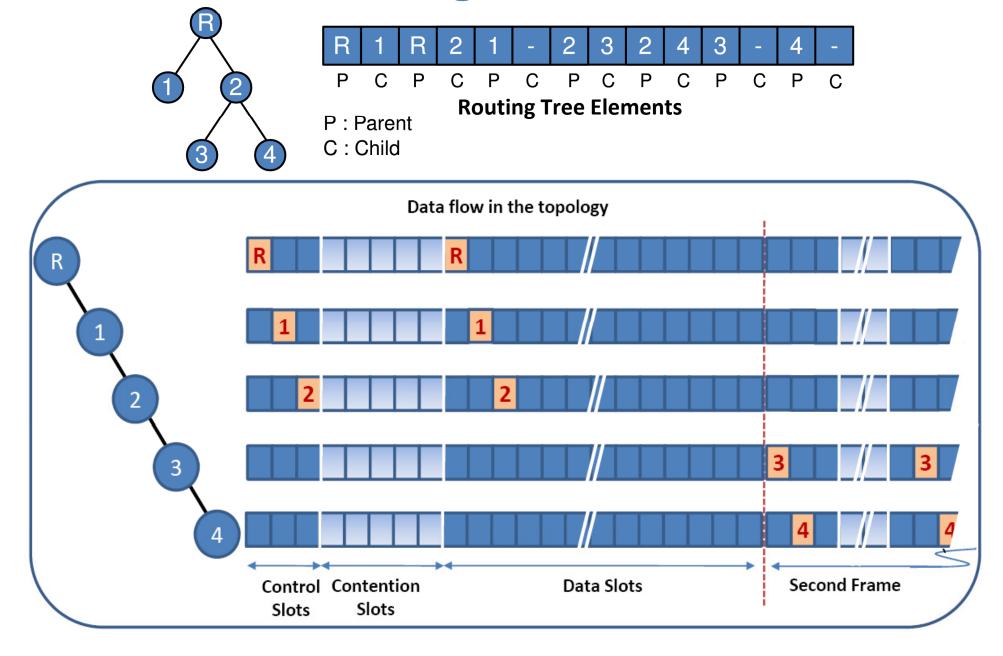

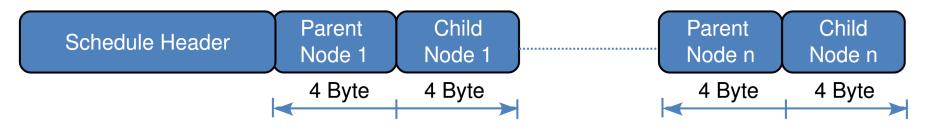

- Multi-hop Schedule Dissemination

- Only root node has authority to create new schedule

- All non-root nodes stores schedule that they receives from their assigned parent for multi-hop transmission

- Data Routing

- Data header attached to data packet is used for routing packet in the network

- Only data header gets modified while packet is being routed

- Routing Tree Elements

- Routing tree elements sent in schedule packet is used by non-root nodes to recreate complete topology

# **Slotting Structure**

#### **Packet Headers**

#### **Data Header**

#### **Schedule Header**

**Routing Tree Elements**

## Framework for TDMA System

- Disabled MAC level acknowledgments Tested

- No RTS/CTS Tested

- Raw packet transmission; no 802.11 frame Tested

- Disabled random/post back-off mechanism Tested

- Tweaked CCA mechanism to always sense channel clear -Tested by Interns (Anupama and Bharat Jain) – Not implemented

- Suppress effect of NAV field and disabled sequence number printing on outgoing packets Tested

- Generating hardware time stamped packets Tested

- Send/Receive packets in monitor mode Tested

- Generation of control packets at MAC layer (in monitor mode) - Tested

- Enabled channel switching from driver code Tested

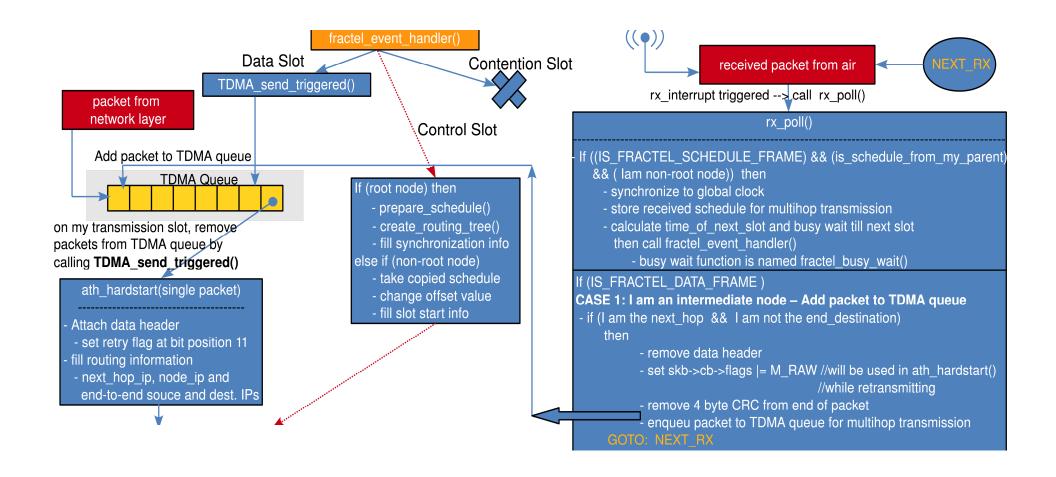

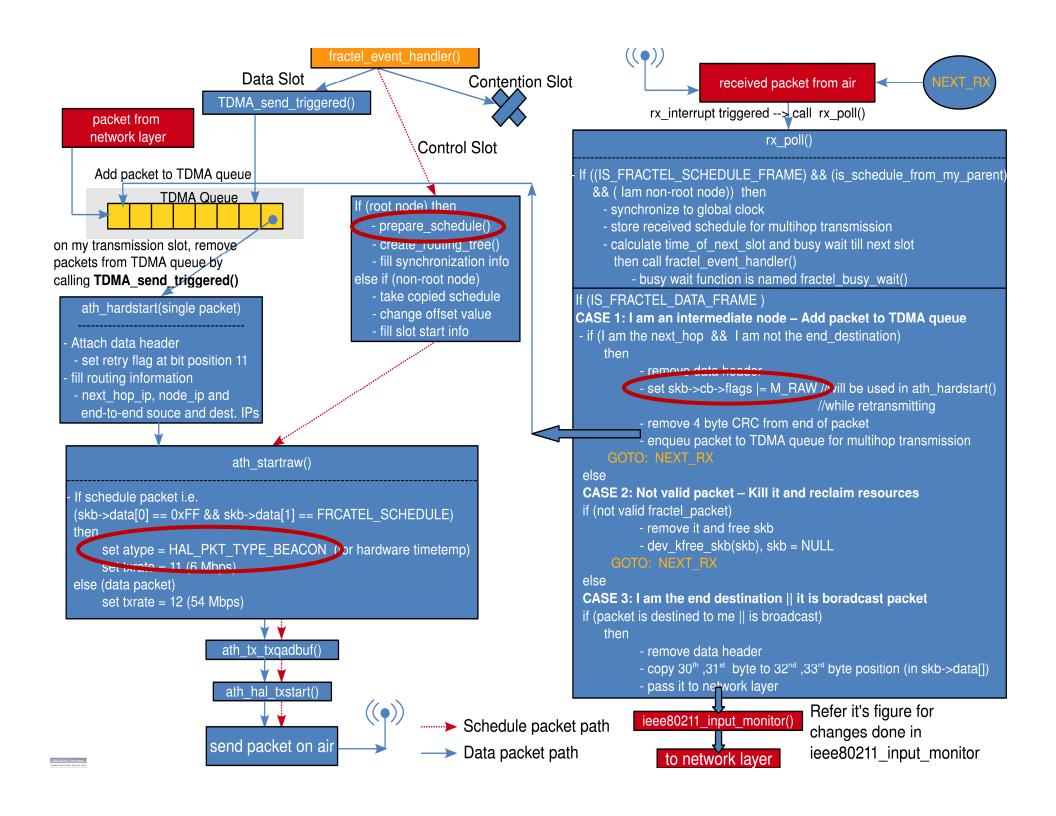

# Multi-hop TDMA System

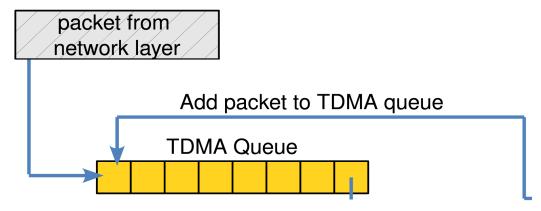

- TDMA queuing mechanism Implemented and Tested

- TDMA slotting structure Implemented and Tested

- Multi-hop packet routing Implemented and Tested

- Plugged in TDMA schedule header and data header along with routing tree elements - Implemented and Tested

- Multi-hop schedule dissemination Implemented and Tested

- Multi-hop time synchronization Implemented and Tested

- Node join mechanism Not Implemented

- Multiple queue implementation Not Implemented

- Packet Filtering based on destination MAC address and discarding packet with CRC and PHY error - Tested

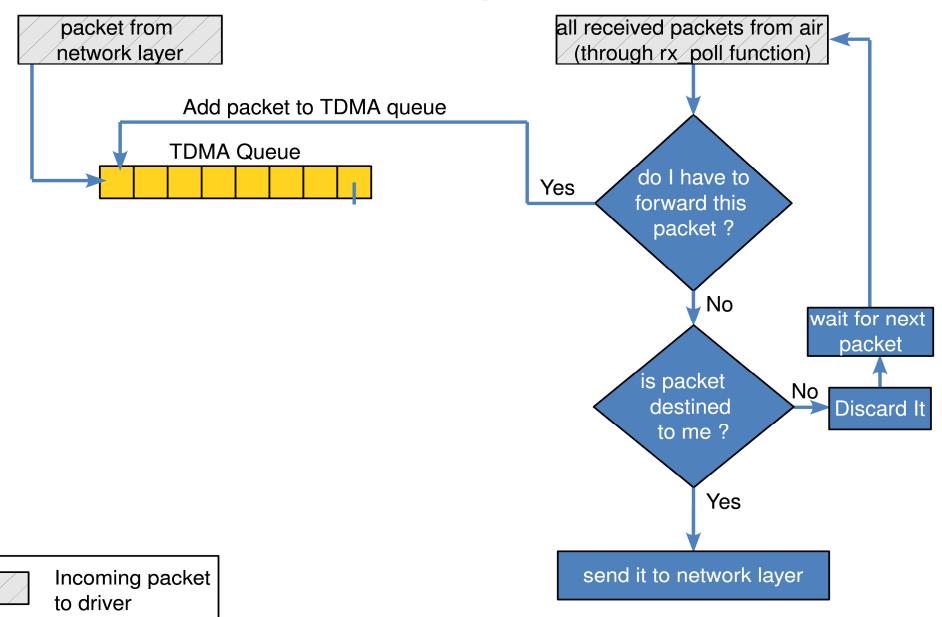

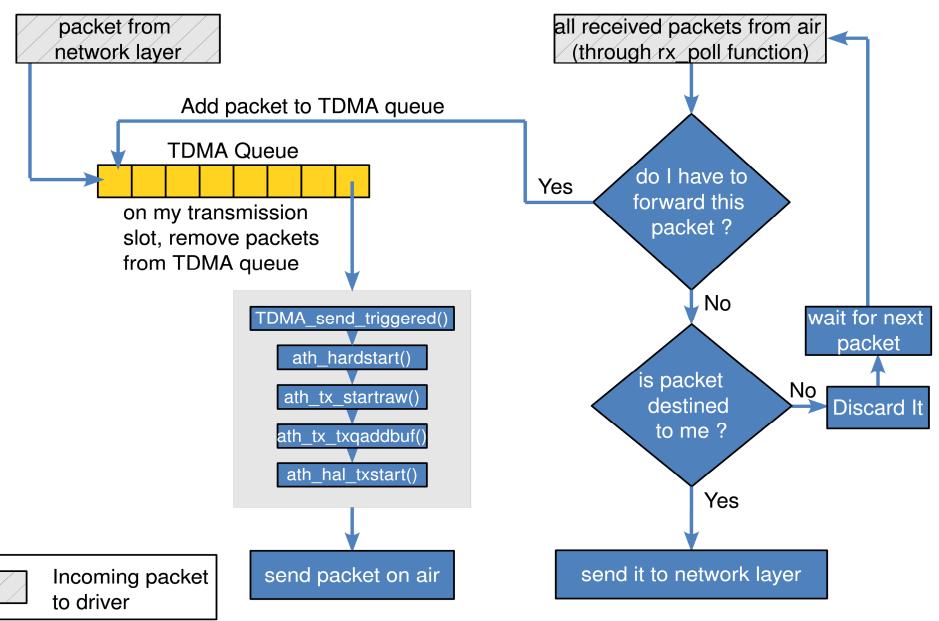

# TDMA Queuing Mechanism

# **TDMA Queuing Mechanism**

# TDMA Queuing Mechanism

## **TDMA Slotting Structure**

### **Problems Faced**

- Monitor mode communication

- Disabling NAV field effect

- Disabling sequence number stamping by hardware

- Enabled receive side path for normal communication

- Hardware time stamping

- Tweaking the hardware to consider schedule packet as 802.11 beacon

- Raw packet generation at MAC layer

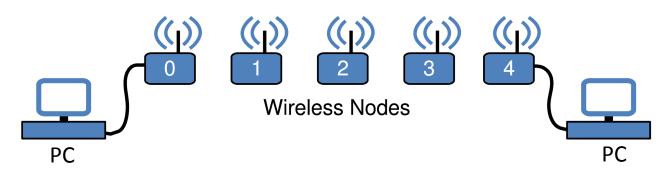

### **Experiment Setup**

| Description         | Bytes | Time (µsec) |

|---------------------|-------|-------------|

| UDP Payload         | 1470  | 217.77      |

| UDP Header          | 8     | 1.185       |

| IP Header           | 20    | 2.962       |

| Ethernet Header     | 14    | 2.074       |

| CRC Trailer         | 4     | 0.592       |

| Fractel Data Header | 32    | 4.740       |

| PLCP Header         | -     | 20          |

| Total               | -     | 249.767     |

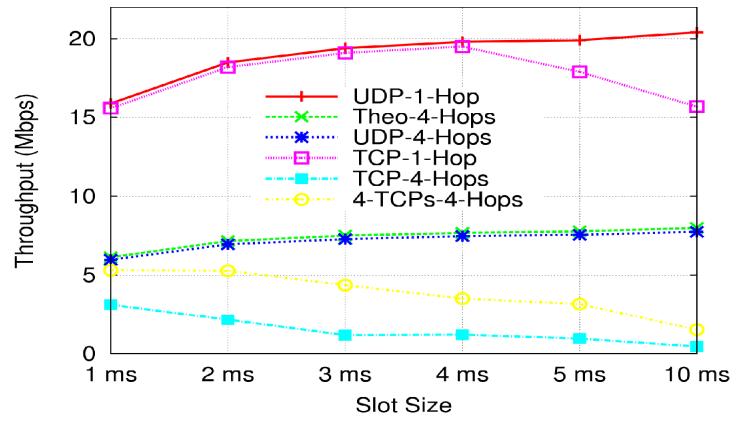

#### **Theoretical UDP throughput for 4-Hop-2msec-slot**

Slot size =  $1900\mu s$  (2000 –  $100\mu s$  guard band)

Packets/slot = 1900/249.767 = **floor(7.607)** = 7

Packets/sec = (frames/sec) \* (# of slots/frame) \* (pkts/slot) = 5 \* (87/5) \* 7 = 609

Throughput =  $609 * 1470 * 8/(10^6) = 7.16$ Mbps

**Transmission Rate: 54Mbps**

3 control, 8 contention and 92 data slots

Theoretical Throughput = 7.16 Mbps Experimental Throughput = 6.93 Mbps

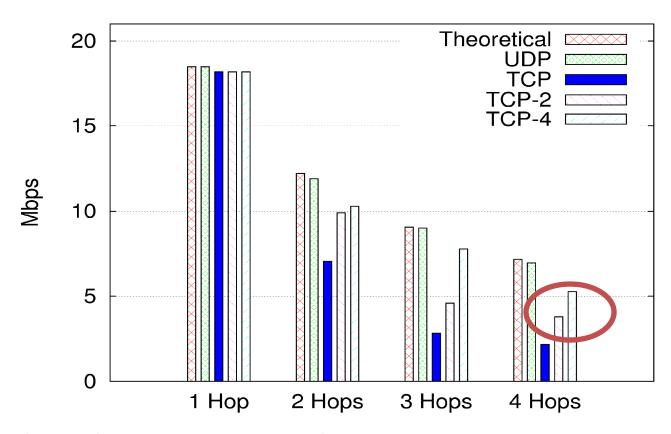

# Results – Throughput Vs Hops

- UDP throughput decreases with increasing Hops

- TCP throughput decreases more drastically with increasing Hops

- large RTT

- No per link retransmission

- Multiple TCP connection though gives better performance

# Results – Throughput Vs Slot Size

- UDP throughput increases with increase in slot size

- Reduced overhead

- TCP throughput decreases with increase in slot size

- large RTT

- less effect of reduced overhead

- TCP gives good performance for small slot size

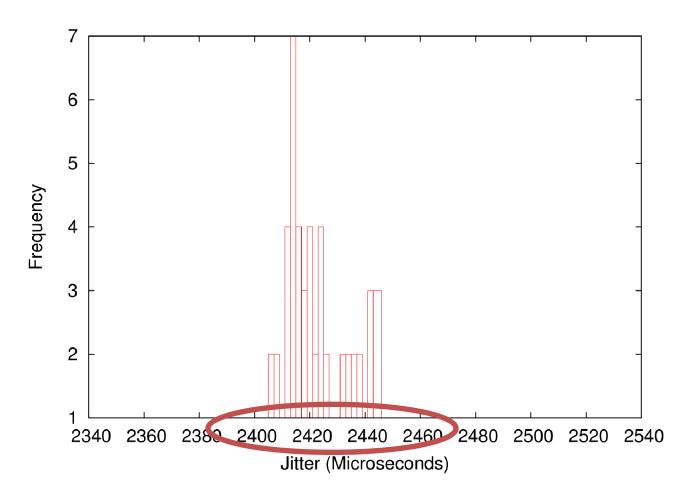

### Results – Jitter for 4-Hop-5ms slot size

Observed jitter for 60 sec UDP connection on 4-Hop-5ms slot size was less then 2.5 msec

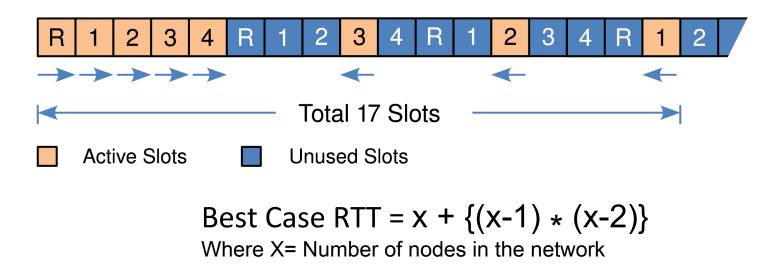

#### Results - Justification for RTT

- Theoretical best case RTT for 4-Hop topology with 2msec slot size is @ 34 msec (17slots \* 2msec/slots)

- We observed very close RTT value during our experimentation

## Implications of Results

- The observed UDP throughput is very close to the theoretically calculated value.

- The throughput for single-TCP connection is quite low for multiple hops but multiple-TCP connections together can provide good performance.

- The observed jitter value is very small even for multihop topology.

- Avenues exist for e-learning through video conferencing, low cost telephony and internet access desirable for rural areas

### Work Done 1 of 2

#### Stage 1

- Understanding madwifi driver

- Understanding Transmit and Receive path in monitor and Ad-hoc mode

- Prototype TDMA implementation in Ad-hoc mode

#### • Stage 2

- Monitor mode communication

- Disabling CSMA mechanism

- Generating packets at MAC layer

- Enabling channel switching

- Implementing TDMA frame structure

- Raw packet transmission; no 802.11 frames

### Work Done 2 of 2

#### • Stage 3

- Corrected faulty TDMA queuing mechanism (from stage2)

- TDMA slotting structure

- Multi-hop packet routing

- Multi-hop schedule dissemination

- Multi-hop time synchronization

#### Future Work

- Node Join Mechanism

- Multiple TDMA queues

- Design and Implementation of Scheduler

### Conclusion

- Modified madwifi device driver

- Implemented Multi-hop TDMA system with

- Schedule dissemination

- Time synchronization

- Carried out extensive experimentation with varying slot size and hops

- Gives very good results while playing videos and making voice calls

- Still lot of work need to be done before live deployment

Thank You!